# Rotational Abstractions for Verification of Quantum Fourier Transform Circuits

1<sup>st</sup> Arun Govindankutty Department of Electrical and Computer Engineering

North Dakota State University

Fargo, USA

arun.g@ndsu.edu

2<sup>nd</sup> Sudarshan K. Srinivasan Department of Electrical and Computer Engineering North Dakota State University

Fargo, USA

sudarshan.srinivasan@ndsu.edu

3<sup>rd</sup> Nimish Mathure Department of Electrical and Computer Engineering North Dakota State University

Fargo, USA

nimish.mathure@ndsu.edu

Abstract-With the race to build large-scale quantum computers and efforts to exploit quantum algorithms for efficient problem solving in science and engineering disciplines, the requirement to have efficient and scalable verification methods are of vital importance. We propose a novel formal verification method that is targeted at Quantum Fourier Transform (QFT) circuits. QFT is a fundamental quantum algorithm that forms the basis of many quantum computing applications. The verification method employs abstractions of quantum gates used in OFT that leads to a reduction of the verification problem from Hilbert space to the quantifier free logic of bit-vectors. Very efficient decision procedures are available to reason about bit-vectors. Therefore, our method is able to scale up to the verification of OFT circuits with 10,000 qubits and 50 million quantum gates, providing a meteoric advance in the size of OFT circuits thus far verified using formal verification methods.

Index Terms—Formal verification, Quantum algorithms, Quantum computing, Quantum Fourier transform, Quantum circuit verification.

# I. INTRODUCTION

The race to build large scale Quantum computers with 1,000 qubits and beyond is in full steam [1] [2]. The IBM Condor quantum computer with 1,000 qubits is expected to be released in 2023 [3]. After Condor, IBM plans to use chip-to-chip couplers to build even larger quantum computing systems [4], with a goal of building a system with 1 million qubits [5]. Google's road map is to built a quantum computer with 1 million qubits as well in the near future [6]. There are numerous other quantum computers being developed by corporations such as Xanadu, Rigetti, IonQ, and D-Wave, to name a few. The development of cryogenic control circuits needed for quantum computing is also accelerated as demonstrated by Intel (Horse Ridge chip) [7], which realizes quantum computing and communication applications [8].

<sup>1</sup>This paper is a preprint of a paper submitted to IET Quantum Computing. If accepted, the copy of record will be available at the IET Digital Library.

The Quantum Algorithm Zoo website tracks algorithms in this domain and currently lists 430 citations of various Quantum algorithms [9].

The 80/20 design rule is well know in computing, i.e., 20% of the design cycle time is spend in the actual design, while 80% is spent in validation and verification. Without verification technologies that can scale, the useful deployment of these large-scale quantum systems will be significantly hampered. It is imperative therefore to develop verification methods for quantum circuits, which is the focus of this work. Formal verification has become a standard in the semiconductor industry with its ability to provide correctness guarantees and flag hard-to-find corner case bugs. There are various formal verification methods proposed for quantum circuits [10].

However, for example, the largest Quantum Fourier Transform (QFT) circuit verified as reported in literature has only 31 qubits [11]. Scalable verification methods are thus the need of the hour.

Contributions: One of the approaches to achieve scalability in formal verification is to develop domain-specific methods. In this work, we target one of the fundamental quantum algorithms, the Quantum Fourier Transform (QFT). In computing and engineering, transformations play a vital role in problem solving and analysis. Quantum computing uses QFT to tackle various problems. QFT is an integral part of numerous quantum algorithms including Shor's factoring algorithm, quantum phase estimation algorithm, and computing discrete logarithm to name a few [12] [13]. The real-world applications where QFT is employed include portfolio optimization in computational finance [14], Monte Carlo pricing of financial derivatives [15], quantum meteorology for building interferometers [16], materials examination and analysis [17], analysis of image data [18] in medical applications, and risk analysis [19] among others.

We have developed a formal verification method that can be

used to efficiently verify Quantum Fourier Transform (QFT) circuits for up to 10,000 qubits and 50 million gates. Our specific contributions are as follows:

- 1) Abstractions of the Hadamard (H) gate and the control rotation gate  $(R_n)$  that exploits the rotational impact of these gates on the incoming qubit.

- A correctness framework that exploits these abstractions and allows the verification problem to be reduced from Hilbert space (complex vector space) to the quantifier free logic of bit-vectors (QF\_BV).

- 3) Theorems with proofs to show that the abstractions are sound, i.e., if the abstract QFT circuit is verified to be correct, then the correctness of the QFT circuit under verification is guaranteed

While we have developed our approach with QFT as the target, the key ideas used in the abstractions can be applied to a much larger class of quantum circuits, which is what we plan to do for future work.

The rest of the paper is organized as follows. Section II covers background on quantum circuits and QFT circuits. Section III overviews the related work on formal methods for verification of quantum circuits. Section IV describes the key contributions of the proposed work, including the gate abstractions and the correctness framework. Section V addresses the correctness of the abstractions and the overall approach. Experimental results are provided and discussed in Section VI. Conclusions and future work are outlined in section VII.

# II. BACKGROUND

In this section, we review background on qubits, quantum gates, and QFT circuits. A detailed description of these topics can be found in [12]. Information in the quantum computing domain is represented by qubits. A qubit is the basic unit of information analogous to a bit in classical computing. In general, qubits are represented by a linear combination of ortho-normal (orthogonal and normalized) vectors  $|0\rangle$  and  $|1\rangle$ . The vectors are linearly independent i.e., we cannot express one as the linear combination of the other. The independent vectors are shown below.

$$|0\rangle = \begin{bmatrix} 1\\0 \end{bmatrix}, and \ |1\rangle = \begin{bmatrix} 0\\1 \end{bmatrix}$$

The above ortho-normal vectors can be used to represent any vectors in the vector space by using vector addition and scaling (linear combination), and thus they are called the *basis vectors*. A standard representation of a qubit  $|q\rangle$  is shown below where,  $\alpha$  and  $\beta$  are complex numbers such that  $\alpha^2 + \beta^2 = 1$ .

$$|q\rangle = \alpha|0\rangle + \beta|1\rangle$$

Quantum gates are unitary operators that act on qubits and produce a required output. A quantum algorithm is a step by step process that utilizes quantum mechanical properties to solve a particular problem. Quantum algorithms are run on computation models for quantum computing and this work is based on the quantum circuit model, which is the most widely used method [20].

QFT is analogous to the Discrete Fourier Transform (DFT) in the classical domain and efficiently performs the quantum mechanical model's Fourier transform. The QFT operates on the input qubit states (ortho-normal basis vectors  $|0\rangle, ....., |N-1\rangle$ ) and transforms them to the corresponding output states. The transformation is shown below [12].

$$|j\rangle \rightarrow \frac{1}{\sqrt{N}} \sum_{k=0}^{N-1} e^{2\pi i jk/N} |k\rangle$$

In the above,  $|j\rangle, N, i$ , and k represents the input qubit, the number of QFT points, imaginary number  $(\sqrt{-1})$ , and the iteration variable, respectively. Here  $N=2^n$ , where n is the number of qubits in the QFT.

In the transformed domain, this resultant state (transformed  $|j\rangle$ ) can be represented as a sum of individual components whose frequencies are integer multiples of  $\frac{2\pi}{N}$ . The same equation can be re-organized to obtain the equivalent transformation happening in each qubit independently, which we exploit in this work.

Implementation of QFT as a circuit can be achieved by a series of cascaded Hadamard (H) gates and controlled rotation  $(R_n)$  gates. The H gates and  $R_n$  gates are defined below.

$$\mathbf{H} = \frac{1}{\sqrt{2}} \begin{bmatrix} 1 & 1\\ 1 & e^{\pi i} \end{bmatrix} = \frac{1}{\sqrt{2}} \begin{bmatrix} 1 & 1\\ 1 & -1 \end{bmatrix}$$

$$\mathbf{R}_n = \begin{bmatrix} 1 & 0 \\ 0 & e^{2\pi i/2^n} \end{bmatrix}$$

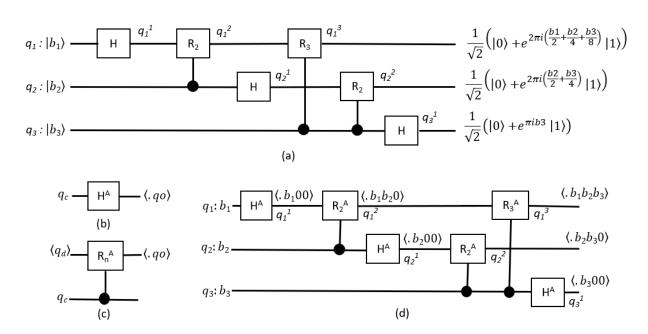

The H gate introduces equal superposition of the input basis vectors for the qubit. The  $R_n$  gates are responsible for the frequency harmonics. QFT circuits are constructed by first applying the H gate to all qubits. Qubit 1 of a QFT circuit with m qubits should have gates  $R_2$ , ...,  $R_m$  acting on it, with control inputs qubit 2, ..., qubit m taken before the H gate is applied to the control qubits, respectively. Qubit 2 should have gates  $R_2$ , ...,  $R_{m-1}$  acting on it with control inputs qubit 3, ..., qubit m taken before the H gate is applied, respectively, and so on. Figure 1(a) shows the transformations happening while QFT is performed on a 3 qubit system.

## III. RELATED WORK

Formal verification of quantum algorithms and circuits has been an active area of research. In this section, we overview these related works and how they contrast with our approach. The main takeaway is that the approaches have not demonstrated the efficiency and scalability that we have been able to achieve. In this sense, our approach is a meteoric advance in the size of quantum circuits thus far verified.

Yamashita and Markov [22] have proposed an equivalence checking approach for quantum circuits. In equivalence checking, the circuit to be verified is compared with a reference

Fig. 1. (a) 3-qubit QFT circuit [21]. (b) Abstract Hadamard gate. (c) Abstract rotation gate. (d) 3-qubit QFT abstract circuit representation.

circuit. There are two prominent contrasts with our approach. The first contrast is related to equivalence checking in general, where a golden (already verified, trusted) circuit is required as the reference circuit. For example, to verify a QFT circuit with 10,000 qubits and 50 million gates, a trusted QFT circuit of the same size is required. Therefore, to enable equivalence checking, methods that can verify functional correctness of a given circuit is mandatory. This is the gap that we address. Equivalence checking is useful in synthesis optimizations. Our approach is property based and does not require a reference circuit of the same size for verification. If a QFT circuit with 10,000 qubits and 50 million gates satisfies our proposed correctness property, it is guaranteed to be correct. The second contrast is that if they are not able to reduce the problem to a boolean space, then a hybrid approach is used [23], where the verification problem is solved in the Hilbert space. We use rotational abstractions to reduce the problem fully to a Boolean space, solvers for which are orders of magnitude more efficient and scalable. We also exploit the fact that our approach is domain-specific to QFT circuit verification to enable this. The largest circuits they verified have 5,000 gates and requires about 59 seconds. In contrast, we are able to verify circuits with 8,000 gates in 0.04 seconds, 5 million gates in about 60 seconds, and 50 million gates in 2,380 seconds.

Amy [11] use complex path-sums to model quantum gates for verification. They perform reductions on the resulting circuit, which are implemented using rewrite rules. The reductions are performed using the Haskell theorem prover. The rewrite rules are guaranteed to reduce the circuit to a normal form, which is then used to check correctness. They verify a 16-qubit and a 31-qubit QFT, which required 1.250 seconds and 16.020 seconds for circuits without errors, respectively. In contrast, our approach required 0.02 seconds and 0.03 seconds for 16-qubit and 32-qubit QFT circuits,

respectively. They employ a dyadic arithmetic technique, the current implementation of which causes an integer overflow for QFT circuits larger than 31 qubits. Therefore, with this current implementation, they are unable to handle QFT circuits larger than 31 qubits. We are able to handle upto 10,000 qubits.

Liu et al. [24] formalize quantum hoare logic in the Is-abelle/HOL theorem prover and use it to prove the correctness of Grover's search algorithm for infinite size input. They report that the proof required 5 person months of effort. They do not describe how this proof can be used to verify a given quantum circuit that implements Grover's algorithm. In contrast, our approach is fully automated for verification of any QFT circuit. They have not addressed QFT verification.

Feng et al. [25] have developed a model checking algorithm that can check the Quantum CTL (QCTL) properties on quantum Markov chains. The method is used to check the correctness of the BB84 protocol when n=1, the corresponding circuit for which has 8 qubits and 24 quantum gates. They have not addressed QFT verification either.

# IV. ROTATIONAL ABSTRACTIONS

There are three key ideas in developing the abstractions for the Hadamard (H) gate and the controlled rotation  $(R_n)$  gate.

The first key idea is with regard to the basis vectors. If a QFT circuit works correctly when the input qubits are the basis vectors  $|0\rangle$  or  $|1\rangle$ , then the circuit is guaranteed to work correctly for any qubit inputs [26]. Therefore, for verification purposes, we only consider the cases where the input qubits are  $|0\rangle$  or  $|1\rangle$ .

The second key idea is with regard to quantum gates and is as follows. If the input qubits are limited to basis vectors, then both the H gate and the  $R_n$  gate can be modelled as gates causing rotation on the basis vectors. The H gate has only one input. We call this the control input  $q_c$  as shown in Figure 1(b),

because if the input is  $|1\rangle$ , then the H gate function can be represented as a rotation on  $|1\rangle$ . If this control input is  $|0\rangle$ , then no rotation is performed. The  $R_n$  gate has two inputs (control and data) and one output, we call the control input  $q_c$ , the data input  $q_d$ , and the output  $q_o$  (as shown in Figure 1(c)). If  $q_c$  is  $|1\rangle$ , then  $R_n$  performs a rotation on  $q_d$ . Otherwise, if  $q_c$  is  $|0\rangle$ , then no rotation is performed.

The third key idea is with regard to the amount of rotation performed by the quantum gates on data input qubits and the resulting output qubit states, and is as follows. The H gate induces a  $\pi$   $(2\pi/2)$  rotation on  $|1\rangle$  and does not rotate  $|0\rangle$ . The  $R_n$  gate induces a  $2\pi/2^n$   $(\pi/2^{n-1}$ ) rotation on  $|1\rangle$  and does not rotate  $|0\rangle$ . For examle,  $R_4$  induces a rotation of  $\pi/8$ . Thus, the rotation performed by the gates on  $|1\rangle$  are negative powers of 2 with reference to  $2\pi$ .

The QFT circuit structure is such that the control inputs to the quantum gates are always initial qubit states and are used only to make the decision, whether to rotate or not.

Thus, we can abstract the basis vector input values  $|0\rangle$  and  $|1\rangle$  using Boolean values 0 and 1.

The qubits once transformed by these rotations are input to the next quantum gate and finally the output state of the circuit.

If the  $2\pi i$  term is factored out of the exponent, the final output state of each qubit (after transformation) can be abstractly represented using fractional bit-vectors that essentially capture the amount of rotation on  $|1\rangle$ . The fractional bit-vector  $\langle .b_1b_2b_3\rangle$  corresponds to rotation value  $2\pi*(b_1*2^{-1}+b_2*2^{-2}+b_3*2^{-3})$ . For example, the bit-vector  $\langle .101\rangle$  corresponds to rotation value of  $2\pi(1/2+0+1/8)$ . Abstractions of the H gate and the  $R_n$  gate can be obtained by defining their rotational impact on the fractional bit-vectors, and an abstracted QFT circuit can be obtained by using these abstracted gates. In a QFT circuit with m qubits, the smallest amount of rotation will be  $2\pi/2^m$ . Therefore, the fractional bit-vectors used to represent qubits in the abstracted QFT circuit will have to have m bits.

The abstract H gate is defined below and has one input qubit  $q_c$ , which is Boolean type. Output qubit  $q_o$  is a bit-vector of size equal to m, the number of qubits.

**Definition 1.** (Abstract Hadamard Gate) If  $q_c$ =1, then  $q_o \leftarrow \langle .100...0 \rangle^m$ , else  $q_o \leftarrow \langle .000...0 \rangle^m$ .

The abstract  $\mathbf{R}_n$  gate is defined below and has two qubit inputs  $q_c$  and  $q_d$ . The control input  $q_c$  is type Boolean, the data input  $q_d$  and the output qubit  $q_o$  are both fractional bitvectors of size m, the number of qubits.

**Definition 2.** (Abstract  $R_n$  Gate) If  $q_c$ =1, then  $q_o \leftarrow q_d +_m \langle .00..01_{m-n}0...0 \rangle^m$ , else  $q_o \leftarrow q_d$ .

In the above,  $+_m$  represents fixed-point modulo addition w.r.t m. The abstracted QFT circuit is obtained by replacing the H gates and  $R_n$  gates of the original circuit with the abstracted gates. Input qubits are declared as type Boolean and all other qubits are declared as type bit-vector of size m. The abstracted QFT circuit with 3 qubits is shown in Figure 1(d). When the abstract H gate is applied, the qubits at the

output of the H gates of the QFT circuit in Figure 1(d) will have the following values:

$$q_1^1 \leftarrow \langle .b_1 00 \rangle$$

$$q_2^1 \leftarrow \langle .b_2 00 \rangle$$

$$q_3^1 \leftarrow \langle .b_3 00 \rangle$$

The QFT correctness property is given next. Let QFT-Abs<sub>i</sub>( $b_1$ ,  $b_2$ , ...,  $b_m$ ) denote the output state of the  $i^{th}$  qubit of an abstracted version of a QFT circuit, where m is the number of qubits and  $b_1$ ,  $b_2$ , ...,  $b_m$  are Boolean variables.

**Property 1.** (QFT Correctness Property) A QFT circuit is functionally correct if, for all  $1 \le i \le m$ , i is an integer, QFT-Abs<sub>i</sub>(b<sub>1</sub>, b<sub>2</sub>, ..., b<sub>m</sub>) =  $\langle .b_ib_{i+1}...b_m0...0\rangle^m$ .

Based on the correctness property above, for the QFT circuit from Figure 1(a) to be correct, the state of qubits at the output should be as follows:

$$q_1^3 = \langle .b_1b_2b_3 \rangle$$

$$q_2^3 = \langle .b_2b_30 \rangle$$

$$q_3^3 = \langle .b_300 \rangle$$

The abstracted gates, abstracted QFT circuit, and Property 1 are expressible in the Quantifier Free logic of Bit Vectors (QF\_BV). A number of SMT solvers exist that can very efficiently check properties in this logic. Therefore, verification of a given QFT circuit can be performed by encoding the abstracted circuit and correctness property in this logic (using the SMT\_LIB language). An SMT solver will check the property automatically and indicate if the property is satisfied or not. If the property is satisfied, then the QFT circuit is guaranteed to be correct (as will be established in the next section). If the property is not satisfied, the tool will generate a counter example, which can be used to trace the error(s) in the circuit.

## V. Abstraction Correctness

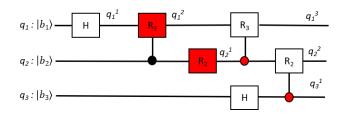

Fig. 2. QFT circuit showing error scenarios.

In this section, we provide a proof of correctness of our verification approach. The overall approach is that we enumerate through all possible classes of errors in QFT circuits and show how the verification approach will flag each error class. The error classes are depicted in Figure 2. We call bit-vector values as data values as well.

TABLE I VERIFICATION RESULTS

| QFT Benchmark |            | Correct Circuit |            | Incorrect Gate Error |          |                     |          | Incorrect Control Error |          |                     |          |

|---------------|------------|-----------------|------------|----------------------|----------|---------------------|----------|-------------------------|----------|---------------------|----------|

|               |            | No Error        |            | Error Depth          |          |                     |          | Error Depth             |          |                     |          |

|               |            |                 |            | Gate-2               |          | Gate-n              |          | Gate-2                  |          | Gate-n              |          |

|               |            | Verificat       | ion Stats. | Verification Stats.  |          | Verification Stats. |          | Verification Stats.     |          | Verification Stats. |          |

| Qubits(n)     | Gates      | M(MB)           | T(s)       | M(MB)                | T(s)     | M(MB)               | T(s)     | M(MB)                   | T(s)     | M(MB)               | T(s)     |

| 16            | 136        | 19.0            | 0.02       | 27.2                 | 0.04     | 27.3                | 0.02     | 19.0                    | 0.01     | 27.2                | 0.02     |

| 32            | 528        | 19.0            | 0.03       | 27.2                 | 0.02     | 27.5                | 0.02     | 19.0                    | 0.02     | 19.0                | 0.01     |

| 64            | 2,080      | 19.0            | 0.03       | 27.3                 | 0.03     | 27.6                | 0.02     | 19.1                    | 0.02     | 19.1                | 0.03     |

| 128           | 8,256      | 19.3            | 0.04       | 27.4                 | 0.07     | 27.9                | 0.04     | 19.3                    | 0.03     | 19.3                | 0.02     |

| 256           | 32,896     | 20.1            | 0.19       | 27.7                 | 0.06     | 28.6                | 0.06     | 20.0                    | 0.08     | 20.0                | 0.08     |

| 512           | 131,328    | 22.1            | 0.26       | 28.3                 | 0.29     | 29.8                | 0.2      | 22.2                    | 0.29     | 22.2                | 0.2      |

| 1,024         | 524,800    | 29.1            | 1.37       | 29.5                 | 0.77     | 32.2                | 0.92     | 29.5                    | 1.46     | 29.5                | 1.29     |

| 2,048         | 2,098,176  | 56.1            | 9.85       | 56.9                 | 5.52     | 73.7                | 5.87     | 56.9                    | 9.66     | 56.9                | 9.47     |

| 4,096         | 8,390,656  | 169.3           | 95.75      | 169.6                | 51.78    | 203.3               | 53.57    | 169.6                   | 73.65    | 169.6               | 79.68    |

| 8,192         | 33,558,528 | 592.1           | 1,109.0    | 593.6                | 640.53   | 596.2               | 643.9    | 593.6                   | 641.03   | 593.6               | 639.57   |

| 10,000        | 50,005,000 | 888.7           | 2,379.88   | 890.7                | 1,523.99 | 894.5               | 1,568.79 | 890.6                   | 1,571.29 | 890.6               | 1,524.65 |

**Lemma 1.** If a QFT circuit has an error, where an incorrect input is fed to an H gate, verification of the abstracted version of the QFT circuit will either generate a type error or will not satisfy Property 1.

If the input to the abstract H gate is a bit-vector input, this will be flagged as a type error as the H gate expects a Boolean input. If Boolean input qubit  $b_j$  is expected whereas  $b_k$  is fed for qubit  $q_j$ , then the LHS of Property 1 for  $q_j$  will be  $\langle .b_k... \rangle$  and RHS will be  $\langle .b_j... \rangle$ . Therefore, Property 1 will not be satisfied.

**Lemma 2.** If a QFT circuit has an error, where an incorrect input is fed to an  $R_n$  gate, verification of the abstracted version of the QFT circuit will either generate a type error or will not satisfy Property 1.

If a control value is fed to the data input of an  $R_n$  gate or if a data value is fed to the control input of an  $R_n$  gate, a type error will be generated. If  $b_j$  is expected whereas  $b_k$  is fed for the control input of an  $R_n$  gate acting on qubit  $q_j$ , then the LHS of Property 1 for  $q_j$  will be  $\langle ....b_k... \rangle$  and RHS will be  $\langle ....b_j... \rangle$ . Therefore, Property 1 will not be satisfied. If an incorrect data value is fed to an  $R_n$  gate, this will result in a missing  $R_n$  gate on a qubit and this case is dealt with subsequently.

The error above is shown in Figure 2.  $R_3$  gate with input  $q_1^2$  should have  $b_3$  as its control input. Instead  $b_2$  is erroneously fed as the control input.

**Lemma 3.** If a QFT circuit has an error, where an H gate is missing on a qubit or there is more than one H gate acting on a qubit, verification of the abstracted version of the QFT circuit will generate a type error.

In the abstracted version of a QFT circuit, the input of an H gate is a control value and the output is a data value. Thus, if there is more than one H gate acting on a qubit, the H gates after the first one will receive data inputs and this will result in a type error. If there are no H gates acting on a qubit, the subsequent  $R_n$  gates will not get a data value at its data input and this will again result in a type error.

An example of a missing H gate error is shown in Figure 2. The H gate on  $q_2$  is missing.

**Lemma 4.** If a QFT circuit has an error where an incorrect set of  $R_n$  gates are acting on a qubit, i.e., required  $R_n$  gates are missing or additional  $R_n$  gates are present or both, verification of the abstract version of the QFT circuit will not satisfy Property 1.

Qubit 1 of a QFT circuit with m qubits should have gates  $R_2$ , ...,  $R_m$  acting on it. Qubit 2 should have gates  $R_2$ , ...,  $R_{m-1}$  acting on it and so on. Thus, there is only one  $R_n$  gate of a certain n value required to act on each qubit. If a required  $\mathbf{R}_n$  gate is missing, then its rotational impact on the fractional bit-vector value abstracting the qubit will not be observed in Property 1. If a qubit has additional erroneous  $R_n$  gates acting on it, then the required rotation of the qubit will be incorrect and this will be reflected on the final fractional bit-vector value of the qubit. In both the above cases, Property 1 will not be satisfied. Note that an  $R_n$  gate can be replaced with two  $R_{n-1}$ gates, with the same control inputs. For example, R2 can be substituted with two R<sub>3</sub> gates. If the total rotational impact of a sequence of  $R_n$  gates is what is expected, even though it does not conform with the  $R_n$  gate sequence described above, Property 1 will be satisfied because the fractional bit-vector abstraction accurately captures the rotations.

An example of an incorrect  $R_n$  gate is shown in Figure 2, where the gate on  $q_1^1$  should be  $R_2$  instead of  $R_3$ .

**Lemma 5.** If a QFT circuit has a combination of errors from the error classes described in Lemmas 1-4, verification of the abstracted version of the QFT circuit will generate a type error or will not satisfy Property 1.

As can be seen from Lemmas 1-4, the effect that flags each error class is disjoint, i.e., there is no overlap in these effects for type errors or Property 1. Thus a combination of errors will also be flagged as a type error or will not satisfy Property 1.

**Theorem 1.** (QFT-Rotational Abstraction Correctness) If a QFT circuit has an error, verification of the abstracted version of the QFT circuit will generate a type error or will not satisfy Property 1.

A QFT circuit has only two types of gates, the H gate and the  $R_n$  gate. Based on this, there are only four classes of

errors possible: Incorrect input to a H gate, incorrect input to an  $R_n$  gate, missing or additional H gates in the circuit, and incorrect set of  $R_n$  gates acting on a qubit. The fifth case of an erroneous QFT circuit is any combination of the above. From Lemmas 1-5, we see that in all the above cases, verification of the abstracted version of the QFT circuit will generate a type error or will not satisfy Property 1.

#### VI. RESULTS AND DISCUSSIONS

Table I gives the verification results. The verification benchmarks were generated by varying the number of qubits in the QFT circuit from 16 qubits to 10,000 qubits. The table gives the number of quantum gates in each of the QFT benchmark circuits as well (column 2: Gates). The verification experiments were conducted on an Intel(R) Core(TM) i9 - 12900K CPU @ 3.2 GHz with 32 GB RAM and Ubuntu 64-bit operating system. The z3 version 4.8.12 SMT solver [27] was used to check Property 1 for all benchmarks.

In the table, "T(s)" indicates verification time in seconds, which is the z3 run time. "M(MB)" gives the z3 run time memory consumption in megabytes. "Correct Circuit" gives the verification statistics for the QFT circuits without errors. For these circuits Property 1 is proved to be satisfied. Property 1 allows for each qubit output to be verified independently. Therefore, the verification of all the qubit output in the circuit were done in parallel and the memory and time reported correspond to the worst case.

"Incorrect Gate Error" are circuits with gates errors and is described as follows. The Gate-2 error here indicates that the  $R_3$  gate is incorrectly acting on qubit 1 instead of  $R_2$ . The Gate-n error here indicates that the  $R_{n-1}$  gate is incorrectly acting on qubit 1 instead of  $R_n$ . "Incorrect Control Error" are circuits with incorrect control input to an  $R_n$  gate. The Gate-2 error here indicates that the  $R_2$  gate in qubit 1 is incorrectly controlled by qubit 3 instead of qubit 2. The Gate-n error here indicates that the  $R_n$  gate in qubit 1 is incorrectly controlled by qubit n-1 instead of qubit n. For the circuits with errors, verification of Property 1 generates a counterexample. The time and memory reported corresponds to the verification of the first qubit output that caused a counterexample to be generated.

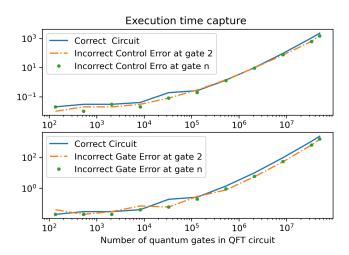

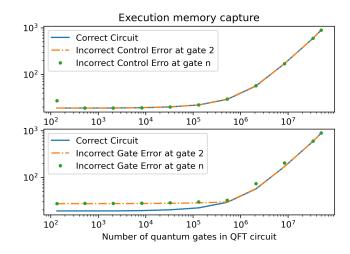

Figures 3 and 4 plot the verification time and memory from Table I versus the number of quantum gates, respectively. In these graphs, both the x-axis and y-axis use a log scale. As can be seen from these graphs, with increase in the number of gates, both memory and verification time increase linearly for both correct circuits and circuits with errors. The most complex circuit with 10,000 qubits and 50 million gates is verified in only about 37 minutes. This demonstrates the high efficiency and scalability of our approach. The time taken to verify circuits with errors is less than that of correct circuits. However, there is not an order-of-magnitude reduction that is often observed in formal verification.

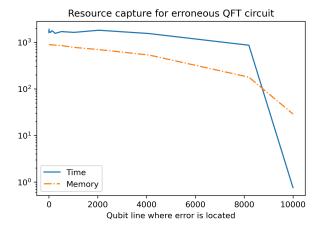

Figure 5 shows both verification time and memory as the position of the gate error is moved from qubit 1 to qubit 10,000 on the QFT circuit with 10,000 qubits. The x-scale increases linearly, whereas the y-scale is logarithmic. The

graph indicates the variation of time and memory with the vertical location of errors. We see that as the error moves from qubit 1 to qubit 10,000, both time and memory reduce exponentially.

Fig. 3. Execution time requirement capture for QFT verification versus quantum gate count. Correct circuit, control input error and value error at qubit positions 2 and 10000 captured for elucidation.

Fig. 4. Execution memory requirement capture for QFT verification versus quantum gate count. Correct circuit, control input error and value error at qubit positions 2 and 10000 captured for elucidation.

### VII. CONCLUSIONS AND FUTURE WORK

Our proposed approach for verification of Quantum Fourier Transform (QFT) circuits achieves a meteoric advance in the efficiency and scalability of quantum circuits thus far verified. We have been able to verify a QFT circuit with 10,000 qubits and over 50 million gates in only about 37 minutes. We exploit the fact that our approach is domain specific to QFT verification. This is a common theme to achieve scalability in formal verification. For example, there are a large number of formal verification techniques dedicated to the verification of multipliers. We also exploit the idea that the rotations performed by the gates are negative powers of 2

Fig. 5. Resource utilization (time and memory) capture versus qubit count for erroneous QFT circuit.

and can therefore be encoded as fractional bit-vectors, thus reducing the verification obligations from Hilbert space to Boolean space. For future work, our goal is to extend these ideas to other quantum algorithms to advance efficiency and scalability of formal verification so as to cope with the size and complexity of quantum hardware roadmaps of the near future.

## REFERENCES

- D. Gottesman and I. L. Chuang, "Demonstrating the viability of universal quantum computation using teleportation and single-qubit operations," <u>Nature</u>, vol. 402, pp. 390–393, 11 1999.

- [2] F. A. et.al., "Quantum supremacy using a programmable superconducting processor," Nature, vol. 574, pp. 505–510, 10 2019.

- [3] G. Jay, F. Ismael, and W. Karl. (2021, 2) Ibm's roadmap for building an open quantum software ecosystem. [Online]. Available: https://research.ibm.com/blog/quantum-development-roadmap

- [4] K. Krewell and T. Research. (2022, 6) The next generation of ibm quantum computers. [On-line]. Available: https://www.forbes.com/sites/tiriasresearch/2022/06/22/the-next-generation-of-ibm-quantum-computers/?sh=5083d463266f

- [5] J. Gambetta. (2022, 5) Expanding the ibm quantum roadmap to anticipate the future of quantum-centric supercomputing. [Online]. Available: https://research.ibm.com/blog/ibm-quantum-roadmap-2025

- [6] J. Porter. (2021,5) Google wants build useful computer by 2029. [Online]. quantum https://www.theverge.com/2021/5/19/22443453/ Available: google-quantum-computer-2029-decade-commercial-useful-qubits-quantum-transistor

- [7] J.-S. Park, S. Subramanian, L. Lampert, T. Mladenov, I. Klotchkov, D. J. Kurian, E. Juarez-Hernandez, B. Perez-Esparza, S. R. Kale, K. T. Asma Beevi, S. Premaratne, T. Watson, S. Suzuki, M. Rahman, J. B. Timbadiya, S. Soni, and S. Pellerano, "13.1 a fully integrated cryocmos soc for qubit control in quantum computers capable of state manipulation, readout and high-speed gate pulsing of spin qubits in intel 22nm ffl finfet technology," in 2021 IEEE International Solid-State Circuits Conference (ISSCC), vol. 64, 2021, pp. 208–210.

- [8] G. Arun and V. Mishra, "A review on quantum computing and communication," in 2014 2nd International Conference on Emerging Technology Trends in Electronics, Communication and Networking, 2014, pp. 1–5.

- [9] S. Jordan. (2021, 2) Quantum algorithm zoo. [Online]. Available: https://quantumalgorithmzoo.org

- [10] M. Lewis, S. Soudjani, and P. Zuliani, "Formal verification of quantum programs: Theory, tools and challenges," <u>CoRR</u>, vol. abs/2110.01320, 2021. [Online]. Available: https://arxiv.org/abs/2110.01320

- [11] M. Amy, "Towards large-scale functional verification of universal quantum circuits," <u>Electronic Proceedings in Theoretical Computer Science</u>, vol. 287, pp. 1–21, 1 2019.

- [12] M. A. Nielsen and I. L. Chuang, Quantum Computation and Quantum Information: 10th Anniversary Edition, 10th ed. USA: Cambridge University Press, 2011.

- [13] E. Sakk, Quantum Fourier Operators and Their Application. IntechOpen. 7 2021.

- [14] P. Rebentrost and S. Lloyd, "Quantum computational finance: quantum algorithm for portfolio optimization," 11 2018.

- [15] P. Rebentrost, B. Gupt, and T. R. Bromley, "Quantum computational finance: Monte carlo pricing of financial derivatives," <u>Physical Review</u> A, vol. 98, p. 022321, 8 2018.

- [16] Z.-E. Su, Y. Li, P. P. Rohde, H.-L. Huang, X.-L. Wang, L. Li, N.-L. Liu, J. P. Dowling, C.-Y. Lu, and J.-W. Pan, "Multiphoton interference in quantum fourier transform circuits and applications to quantum metrology," <u>Physical Review Letters</u>, vol. 119, p. 080502, 8 2017.

- [17] H. Grimm-Strele and M. Kabel, "Fft based homogenization with mixed uniform boundary conditions," <u>International Journal for Numerical</u> Methods in Engineering, vol. 122, pp. 7241–7265, 12 2021.

- [18] A. Geng, A. Moghiseh, C. Redenbach, and K. Schladitz, "Improved frqi on superconducting processors and its restrictions in the nisq era," 10 2021

- [19] S. Woerner and D. J. Egger, "Quantum risk analysis," npj Quantum Information, vol. 5, p. 15, 12 2019.

- [20] A. Barenco, C. H. Bennett, R. Cleve, D. P. DiVincenzo, N. Margolus, P. Shor, T. Sleator, J. A. Smolin, and H. Weinfurter, "Elementary gates for quantum computation," <u>Phys. Rev. A</u>, vol. 52, pp. 3457–3467, Nov 1995. [Online]. Available: <a href="https://link.aps.org/doi/10.1103/PhysRevA.52.3457">https://link.aps.org/doi/10.1103/PhysRevA.52.3457</a>

- [21] R. Muradian. (2011, 3) Quantum fourier transform circuit. [Online]. Available: https://demonstrations.wolfram.com/ QuantumFourierTransformCircuit

- [22] S. Yamashita and I. L. Markov, "Fast equivalence-checking for quantum circuits," 2009. [Online]. Available: https://arxiv.org/abs/0909.4119

- [23] G. F. Viamontes, I. L. Markov, and J. P. Hayes, "Checking equivalence of quantum circuits and states," 2007. [Online]. Available: https://arxiv.org/abs/0705.0017

- [24] J. Liu, B. Zhan, S. Wang, S. Ying, T. Liu, Y. Li, M. Ying, and N. Zhan, "Formal verification of quantum algorithms using quantum hoare logic," in <u>Computer Aided Verification</u>, I. Dillig and S. Tasiran, Eds. Cham: Springer International Publishing, 2019, pp. 187–207.

[25] Y. Feng, N. Yu, and M. Ying, "Model checking quantum markov

- [25] Y. Feng, N. Yu, and M. Ying, "Model checking quantum markov chains," <u>Journal of Computer and System Sciences</u>, vol. 79, no. 7, pp. 1181–1198, 2013. [Online]. Available: https://www.sciencedirect.com/ science/article/pii/S0022000013000780

- [26] F. X. Lin, "Shor's algorithm and the quantum fourier transform," <u>McGill</u> University, 2014.

- [27] L. De Moura and N. Bjørner, "Z3: An efficient smt solver," in Proceedings of the Theory and Practice of Software, 14th International Conference on Tools and Algorithms for the Construction and Analysis of Systems, ser. TACAS'08/ETAPS'08. Berlin, Heidelberg: Springer-Verlag, 2008, p. 337–340.