# MaliGNNoma: GNN-Based Malicious Circuit Classifier for Secure Cloud FPGAs

Lilas Alrahis<sup>\*</sup>, Hassan Nassar<sup>†</sup>, Jonas Krautter<sup>†</sup>, Dennis Gnad<sup>†</sup>, Lars Bauer<sup>†</sup>, Jörg Henkel<sup>†</sup> and Mehdi Tahoori<sup>†</sup> \*New York University Abu Dhabi, Abu Dhabi, United Arab Emirates (UAE)

<sup>†</sup>Karlsruhe Institute of Technology (KIT), Institute for Computer Engineering (ITEC), Karlsruhe, Germany Email: lma387@nyu.edu, {hassan.nassar, jonas.krautter, dennis.gnad, lars.bauer, henkel, mehdi.tahoori}@kit.edu

Abstract—The security of cloud field-programmable gate arrays (FPGAs) faces challenges from untrusted users attempting fault and side-channel attacks through malicious circuit configurations. Fault injection attacks can result in denial of service, disrupting functionality or leaking secret information. This threat is further amplified in multi-tenancy scenarios. Detecting such threats before loading onto the FPGA is crucial, but existing methods face difficulty identifying sophisticated attacks.

We present *MaliGNNoma*, a machine learning-based solution that accurately identifies malicious FPGA configurations. Serving as a netlist scanning mechanism, it can be employed by cloud service providers as an initial security layer within a necessary multi-tiered security system. By leveraging the inherent graph representation of FPGA netlists, MaliGNNoma employs a graph neural network (GNN) to learn distinctive malicious features, surpassing current approaches. To enhance transparency, MaliGNNoma utilizes a parameterized explainer for the GNN, labeling the FPGA configuration and pinpointing the sub-circuit responsible for the malicious classification.

Through extensive experimentation on the ZCU102 board with a Xilinx UltraScale+ FPGA, we validate the effectiveness of MaliGNNoma in detecting malicious configurations, including sophisticated attacks, such as those based on benign modules, like cryptography accelerators. MaliGNNoma achieves a classification accuracy and precision of 98.24% and 97.88%, respectively, surpassing state-of-the-art. We compare MaliGNNoma with five state-of-the-art scanning methods, revealing that not all attack vectors detected by MaliGNNoma are recognized by existing solutions, further emphasizing its effectiveness. Additionally, we make MaliGNNoma and its associated dataset publicly available.

## I. INTRODUCTION

In response to the evolving landscape of high-speed computation demands in the cloud, traditional central processing units (CPUs) and graphics processing units (GPUs) have become inadequate in terms of latency, efficiency, and throughput [1]. To address the increasing performance requirements, field programmable gate arrays (FPGAs) have been integrated into cloud computation platforms. This integration allows users to customize their hardware accelerators for computationally intensive tasks in the cloud. For instance, cloud service providers (CSPs), such as Amazon Web Service (AWS) [2] and Microsoft [3], offer cloud-based FPGAs that clients can rent and customize with their own logic [4]; this model can be referred to as *FPGA-as-a-Service* (FaaS).

As clients have control over programming these FPGAs, multiple security concerns are raised. One prominent example is *fault-injection attacks*, wherein circuits are intentionally configured to induce severe voltage fluctuations, leading to

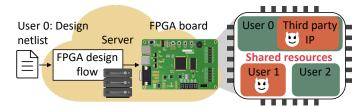

Fig. 1. Cloud FPGA with shared resources and open attack vectors. The threat model involves either a malicious user utilizing the entire FPGA or a malicious third-party IP provider, or in the context of multi-tenancy, a malicious co-tenant. Assuming the cloud provider is trustworthy, malicious entities can manipulate their designs intentionally, leading to fault-injection attacks.

hardware faults. Such faults can either be subtle and cause computation errors, or cause a crash of the FPGA device and therefore denial-of-service (DoS) [5], jeopardizing the entire availability of the system. When evaluating the financial loss for commercial CSPs versus the costs of performing the attack, the cost of the downtime of FPGA infrastructure is  $10 \times$  as much as the costs for the attacker causing the downtime [6]. Such powerful attacks put the CSPs at a severe disadvantage to the attackers and make them potential victims of sabotage [6].

These threats can be even more amplified with the concept of *multi-tenancy*. To meet the performance demands of the FaaS model, large and expensive FPGAs are deployed in the cloud. To enhance cost-efficiency and maximize return on investment for CSPs, it is essential to fully utilize this capacity. When clients with the necessary resource and computing demands are not present, the FPGA fabric can be shared among multiple clients (*tenants*) with smaller resource requirements. Sharing the fabric optimizes the FPGA utilization and makes it more cost-effective for individual users, if less users are capable of utilizing the entire FPGA fabric [7].

Multi-tenancy has not been realized commercially yet, mainly due to security challenges. One of the reasons is the shared power delivery networks of the FPGA fabric among tenants, which can create potential attack vectors [8]. Next to the fault-injection attacks that can crash the FPGAs, *sidechannel attacks* use indirect power measurements to exfiltrate secret information from one tenant's FPGA fabric through a malicious co-tenant [9], [10], [11]. Additionally, more finegrained fault-injection attacks do not only affect the availability of resources, but can also affect data integrity by causing delicate faults that only affect individual bytes. Using that, attacks exist to extract cryptographic secrets [12], [13] or information in neural network accelerators [14]. Further research on this topic is needed to reveal potentially more vulnerabilities and provide effective countermeasures, making multi-tenancy secure and hence feasible. Fig. 1 demonstrates the scenario of cloud FPGAs that support multi-tenancy, with the accompanying threat model explanation.

In this work, we address the security of cloud FP-GAs against fault-injection attacks, while considering multitenancy. Side-channel attacks are not addressed here, but can be solved orthogonal to us – for instance on the level of timing analysis, as suggested in [8]. While we consider multi-tenancy scenarios, our research is not entirely confined to that aspect.

In this context, researchers have explored various protection schemes to enhance the security of cloud FPGA deployments, including architectural modifications to the FPGAs and circuit design enhancements to mitigate vulnerability to faultinjection and side-channel attacks [15], [16]. Nevertheless, ensuring the security of cloud FPGAs necessitates a multitiered defense system that integrates all the aforementioned measures for maximum security. Additionally, the first layer of security in such a system should proactively detect and prevent attacks before loading the user's configuration to the FPGA, thus preventing any potential damage. One effective approach involves a *hypervisor* that checks and allows only benign bitstreams to be loaded onto the FPGA fabric [17] (we refer to such methods as scanning techniques). However, existing scanning methods have serious limitations, as discussed next.

# A. State-of-the-Art and their Limitations

Scanning the Bitstream: Existing methods either reverseengineer the netlist from the bitstream [8], [18], or scan the bitstream directly for malicious signatures [19]. However, in the workflow of cloud FPGAs, users provide a design prior to the bitstream, i.e., a Verilog netlist, out of which the final bitstream needs to be generated by the cloud-hosted electronic design automation (EDA) tools, which also perform respective design rule checking (DRC) [6]. Hence, incorporating a scanning method at DRC level directly fits into the working model of CSPs-that is, the methods should be tailored to scan the netlist itself directly instead of scanning the bitstream. Please note that a bitstream can only be seen as a more obscured netlist [20], it does not provide proper security against intellectual property (IP) theft. A properly encrypted bitstream is indistinguishable from random data, and thus, cannot be checked for security violations.

**Limited Security:** verifies the netlist against a set of predefined rules to detect any potential security vulnerabilities or design errors. However, the existing approaches adopted by CSPs like Amazon, particularly those based on Xilinx FPGAs, primarily focus on detecting various types of ring oscillators (ROs). As a result, they fail to address more sophisticated and complex *attack vectors*,<sup>1</sup> limiting their effectiveness in ensuring comprehensive security for multi-tenant

TABLE I

Capabilities Offered by FPGA Scanning Techniques.

| Techniques   | Self-oscil.<br>attacks | Hidden<br>attacks | Sequen.<br>attacks | Partial<br>designs | Labeling<br>sub-circuits |

|--------------|------------------------|-------------------|--------------------|--------------------|--------------------------|

| Tool of [23] | 1                      | ✓                 | ×                  | ×                  | ×                        |

| Tool of [22] | 1                      | X                 | ×                  | 1                  | ×                        |

| Tool of [19] | 1                      | X                 | 1                  | ×                  | ×                        |

| Tool of [18] | 1                      | X                 | ×                  | 1                  | ✓                        |

| Tool of [8]  | 1                      | X                 | ×                  | 1                  | ×                        |

| MaliGNNoma   | 1                      | 1                 | 1                  | 1                  | 1                        |

✓ denotes detection/labeling capability, while × indicates incapability

FPGAs. Furthermore, existing scanning techniques, such as *FPGAdefender* [18] or the work in [8], are only designed for a limited set of components or very simple FPGAs, which means only elements such as look-up tables (LUTs) and basic arithmetic blocks are considered, but not sequential-based attacks [21]. The capabilities of existing scanning methods in detecting the different types of fault-injection attacks are summarized in Table I. These attacks will be explained in detail in Section II. In this work, we extend the scope of applicability to all available FPGA resources.

**Identifying Malicious Modules:** Labeling the netlist/bitstream as malicious may lack insights and justification. Methods that classify the netlist/bitstream while providing pointers to specific malicious parts are valuable for design analysis. Table I (right-most column) illustrates how not all existing techniques offer this feature.

Machine Learning (ML)-based Detection: Recently, ML techniques have shown promise in scanning bitstreams to identify malicious configurations [22]. However, there is a research gap in investigating netlist-level approaches for FPGA security, as current ML research focuses on scanning the bitstream directly, proving insufficient for use with the CSP workflow. Moreover, it does not provide justification for identifying malicious parts within the configuration. This lack of transparency poses a challenge in offering feedback for the next layer of scrutiny and verification.

# B. Research Challenges Addressed in this Work

ML's capacity to learn attack signatures and generalize to unseen designs is a significant advantage that can lead to addressing the limitations of state-of-the-art scanning solutions. However, it has not been developed to its fullest potential in this context. Our goal is to leverage ML for FPGA netlist scanning, a promising approach that presents a unique set of challenges, which we discuss next.

Traditional ML models are designed to handle fixed-size numerical vectors/matrices. However, netlists inherently possess a non-Euclidean representation and cannot be mapped to vectors without performing feature engineering. Manual feature engineering is prone to errors and highly dependent on the specific dataset at hand. Furthermore, there is no guarantee that it will result in an optimized representation of the data. Hence, it is necessary to develop ML models that can automatically extract optimized vector representations from

<sup>&</sup>lt;sup>1</sup>These attacks employ carefully combined cryptographic cores and powerintensive modules for fault injection.

complicated netlist structures. These representations can then be used for the learning process. Recently, graph neural networks (GNNs) have emerged as a new type of ML that operates on graph-structured data. These networks can automatically learn and represent graphs as *vector embeddings*, capturing each graph's important properties in a trainable manner. Since circuits can naturally be represented as graphs, GNNs have achieved superior performance in solving various circuit-related tasks, including hardware security (e.g., detecting IP piracy [24] and functional reverse engineering [25], [26]) and reliability (e.g., predicting circuit delay degradation due to aging [27]). However, GNNs have not been employed yet in the context of FPGA security.

2) Using ML models as black-box solutions for critical tasks raises *trust and transparency challenges*. Without insights into how and why decisions are made, trusting the model's results can be a concern, impacting the reliability of the classification.

# C. Our Concept and Contributions

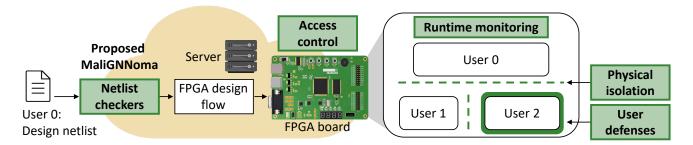

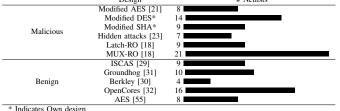

To address the above challenges, we propose the *MaliGN-Noma framework* that identifies different netlist-level malicious FPGA configurations. MaliGNNoma leverages GNNs to accurately classify netlists by capitalizing on their inherent graph structure, as depicted in Fig. 2. Unlike existing methods that focus on checking bitstreams, MaliGNNoma directly operates on netlist graphs. This enables the model to preserve semantic information, extract crucial features, and improve detection capabilities. Additionally, MaliGNNoma aligns seamlessly with the workflow of CSP, where netlists serve as the primary input for generating bitstreams. MaliGN-Noma employs the following techniques:

- 1) We present an ML-based approach for FPGA netlist checking that employs a GNN. In our evaluation, we consider two different GNN architectures and investigate the incorporation of attention layers and dropout. Our aim is to provide insights into the capabilities of GNNs for this task, as this is their first application in such a context. We have constructed our own dataset of FPGA netlists to train the GNN, which we to the research community at the following repository: https://github.com/hassanassar/MaliGNNoma.

- 2) Interpretation: Additionally, we integrate our framework with a state-of-the-art parameterized explainer for GNNs [28]. This explainer, when given a graph (i.e., a netlist), extracts a subgraph (i.e., sub-circuit) that has the most influence on the GNN's predictions. By identifying specific gates contributing to the prediction of a 'malicious' label, MaliGNNoma offers valuable insights for investigation by circuit designers.

**Key Results:** The effectiveness of MaliGNNoma is showcased by training it over a dataset comprising of benign and malicious designs. The benign benchmarks are collected from ISCAS benchmark [29], Berkley benchmark [30], Groundhog benchmark [31], and OpenCores [32]. The malicious designs

# Hypervisor employing MaliGNNoma Highlighting malicious nodes

Fig. 2. High-level view of our work: Identifying malicious FPGA configurations at the netlist-level using graph neural networks (GNNs).

TABLE II

Commonly Used Abbreviations and Notations

| Term                                               | Definition                                                           | Term                                                    | Definition                                                      |

|----------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------|

| $\begin{array}{c} h_v^{(l)} \\ \sigma \end{array}$ | Node $v$ embedding at GNN layer $l$<br>Nonlinear activation function | $egin{array}{c c} N(v) \\ \mathbf{H}^{(l)} \end{array}$ | Neighbors of node $v$ , excluding $v$<br>Node embeddings matrix |

| $\mathbf{x}^{(l)}_{\mathbf{X}}$                    | Aggregated information                                               | L                                                       | Total number of GNN layers                                      |

|                                                    | Node features matrix                                                 | W                                                       | Trainable weight matrix                                         |

|                                                    | Adjacency matrix                                                     | MLP                                                     | Multi layer perceptron                                          |

| $\widehat{\hat{\mathbf{D}}}_{h_G}$                 | Diagonal degree matrix                                               | G                                                       | Graph                                                           |

|                                                    | Graph-level embedding                                                | E                                                       | Edges in G                                                      |

| V                                                  | Nodes in $G$                                                         | N                                                       | Number of nodes in $G$                                          |

| $\hat{y}_G$                                        | Prediction for $G$                                                   | $y_G$                                                   | Ground truth for $G$                                            |

contain state-of-the-art attacks as described in [18], [23], [21], [33]. We crafted the malicious designs based on state-of-theart methodologies, as they are not open-sourced. We evaluated all designs in our dataset on a ZCU102 FPGA Board and confirmed that malicious designs injected faults into neighboring tenants.<sup>2</sup> MaliGNNoma achieves a classification accuracy and precision of 98.24% and 97.88%, respectively. We make MaliGNNoma and associated benchmarks (benign and malicious) available online.<sup>3</sup>

# II. BACKGROUND AND RELATED WORK

Ensuring the security of cloud FPGAs requires a multitiered defense system, as demonstrated in Fig. 3. This system includes netlist checking for malicious implementations, access control between the FPGA processor and peripherals, physical isolation between tenants, and runtime monitoring to detect any suspicious activities [1]. All of these defenses should be supported and implemented by the CSP. Additionally, users can incorporate design-level defenses, such as masking and active defenses, to protect their own designs [15]. All these measures are required to ensure the security of the system against various attacks. Our primary focus is on netlist checking, the first stage of protection.

In this section, we present the necessary background on FPGA-internal attacks, existing countermeasures against them, and information on GNNs, netlist to graph conversion, and the utilization of GNNs for various circuit-related tasks. Table II provides the notations used throughout the paper.

<sup>&</sup>lt;sup>2</sup>The widley-adopted Trust-HUB dataset [34] is for detecting hardware Trojans in application-specific integrated circuits (ASIC). However, we focus on identifying fault-injection attacks in FPGAS (different scope). Integrating this dataset into MaliGNNoma would not be aligned with our objectives.

<sup>&</sup>lt;sup>3</sup>Code:https://github.com/DfX-NYUAD/MaliGNNoma Dataset:https://github.com/hassanassar/MaliGNNoma.

Fig. 3. Multi-tiered defense system for securing cloud FPGAs. Defense mechanisms, highlighted in green, include netlist checking, access control, physical isolation, and runtime monitoring implemented by the CSP. Users can further enhance security with design-level defenses such as masking and active measures.

# A. FPGA-Internal Attacks

Most known FPGA-internal attacks are based on voltage fluctuations or cross-coupling between logically isolated designs, which can be exploited through fault-injection or side-channel attacks, that traditionally have been carried out with test and measurement equipment, while having physical access. On one hand, voltage sensors based on FPGA logic can be used to estimate voltage fluctuations, which are then analyzed to recover secret key information [35], [9] or more recently also information about neural network accelerators [11], [36], [14]. On the other hand, fault-injection attacks cause errors in computation, which can lead to DoS as well as differential fault analysis (DFA) to extract confidential data [5], [13]. We focus on fault-injection attacks, which cause a very high voltage drop through excessive switching activity, that is sufficient to cause timing violations in designs integrated in other partitions of the FPGA.

The first FPGA-internal fault-injection attacks were typically implemented using a large number of ROs (selfoscillating attacks from Table I) that need a combinational loop [5], [13]. Since cloud platforms such as Amazon EC2 F1 integrate a basic check for combinational loops, stealthy RO variants were developed, making detection difficult in the toolchain [37]. Later it was shown that faults can also be caused using access conflicts based on block memory (BRAM) in Xilinx FPGAs [33], and specific ways to configure logic go under the name of glitch amplification [38] to also cause very high voltage variations. In the end, even seemingly benign circuits (sequential attacks from Table I) have been shown able of causing a sufficient voltage drop that results in faulty behavior, which is very stealthy and harder to detect [21], [39]. To increase the stealthiness of the attack, the attackers mix benign circuits with malicious circuits within the same design (hidden attacks from Table I) [23] which makes it also harder to detect.

### B. Existing Countermeasures Against FPGA-Internal Attacks

To prevent FPGA-internal attacks, traditional countermeasures against fault-injection and side-channel attacks can be employed for cryptographic implementations, but come with respectively high overheads. Instead, some runtime countermeasures are more tailored to the needs of FPGAs, such as *hiding* against side-channel attacks [15] or actively trying to prevent fault-injection attacks [40], with mixed effectivity.

Thus, more research was dedicated towards detecting malicious designs before they even get loaded to the FPGA, similar to an *anti-virus* software. Indeed, these existing works also utilize mechanisms similar to detecting malware in software, but instead of code patterns search for patterns in a bitstream that are typical for either side-channel or fault-injection attacks [8]. However, the difficulty is to detect attacks that are based on seemingly benign circuits, for which [8] only considered highfanout as a potential red flag. Later, [18] focused on faultinjection attacks and the various types of malicious powerwasting circuits, but without the goal of detecting variants based on benign circuits.

What these two works have in common [8], [18], is that they are based on reverse engineering and checking the bitstream. Instead, the work in [19] tries to be independent of that, and applies metrics to directly analyze a bitstream for faultinjection attacks. However, it is debatable if an analysis on the raw bitstream is useful, since either cloud providers would be able to get sufficient information from FPGA vendors, or the toolchain itself will have to check it before bitstream generation, which is already enforced by the tool flow needed for the Amazon platform [6].

# C. Graph Neural Networks (GNNs)

A GNN operates by taking a given graph G and encoding it into a vector representation specifically tailored to suit the intended task. In this process, each node within the graph gets represented as a vector known as an "embedding." These embeddings are computed in such a way that nodes with similarities in the graph should ideally be placed close to one another in the embedding space, indicating proximity in terms of distance. The feature vectors assigned to all nodes serve as their initial embedding vectors. Subsequently, the GNN performs "neighborhood aggregation," where each node collects and incorporates messages (i.e., embeddings) from its direct neighbors. These incoming messages are then used to update the node's own embedding based on the received information [41]. These embeddings are crucial for downstream tasks, such as graph classification or other applications, where the learned representations can help in making informed decisions based on the graph structure and its features.

Since circuit netlists resemble graph structures, there has been a growing interest in employing GNNs to solve various circuit problems related to hardware security [42], [43], [26], [25], [24], [44], [45], [46], [47], [48], reliability [49], and EDA [50], primarily focusing on ASIC and analog circuits [27].

In the following sections, we discuss the process of converting a Verilog netlist into a graph (Section II-C1), provide a detailed explanation of the neighbor aggregation operation used in GNNs (Section II-C2), and show how GNN results can be explainable to a human understanding (Section II-C3).

1) Netlist to Graph Conversion: There are several opensource tools that can read a Verilog netlist and convert it into a graph. Specifically, *PyVerilog* is an open-source hardware design processing toolkit that parses Verilog and can construct various graphs, such as data flow graphs (DFGs) and abstract syntax trees (ASTs). This tool is also utilized in state-ofthe-art methods for detecting ASIC hardware Trojans using GNNs [51], [44].

The process begins with converting the netlist into an AST using the yet another compiler-compiler (yacc) lexical analyzer. An AST is a tree-based graph with nodes representing entities such as operators (mathematical, gates, loop, conditional), signals, or signal attributes. The edges represent the relationships between these nodes. To generate the DFG, a module analyzer first extracts a list of modules from the AST. Each module definition includes a signal list for inputs, outputs, and parameters.

Next, the signal analyzer traverses the AST again to collect signal definitions. Signal declarations are analyzed, and the scope of each signal is recorded. Simultaneously, an optimizer resolves constant value definitions, such as parameters and local parameters. Module parameters can be overwritten by their parent module, and the actual hardware structure dependent on these parameters becomes fixed once they are determined.

By utilizing the analysis results from the optimizer, the actual parameters for each module instance and the entire module hierarchy are determined. Finally a bind analyzer generates a DFG for each signal, with each signal serving as the root node. Finally, the signal DFGs are merged to form the resulting graph denoted as G = (V, E). The DFG represents data dependencies, where nodes in V correspond to signals, constant values, and operations like XOR, AND, and concatenation. The edges E depict the data dependency relations between pairs of nodes. The adjacency matrix  $\mathbf{A} \in \{0, 1\}^{N \times N}$  is constructed from E, where  $\mathbf{A}_{u,v} = 1$  iff  $(i, j) \in E$ . N denotes the number of nodes in the graph, i.e., |V|.

2) GNN Architectures: The GNN neighborhood aggregation operation involves two main functions: Aggregate and Update, which are repeated for a pre-determined number of layers L. During each iteration l, the process updates the node embeddings matrix  $\mathbf{H}^{(l)}$  based on the node representations  $h_v^{(l-1)}$  from  $\mathbf{H}^{(l-1)}$ , where  $\mathbf{H}^{(0)}$  is the same as the feature matrix  $\mathbf{X}$ , as given by:

$$a_v^{(l)} = \text{Aggregate}^{(l)}(\{h_u^{(l-1)} : u \in N(v)\})$$

(1)

$$h_v^{(l)} = \text{Update}^{(l)}(h_v^{(l-1)}, a_v^{(l)})$$

(2)

For each node v, the embedding after l iterations is denoted as  $h_v^{(l)} \in \mathbb{R}^{C^l}$ , where  $C^l$  represents the embedding dimension at layer l. The Aggregate operation collects the features, i.e., messages, of the neighboring nodes N(v) to generate an aggregated feature vector  $a_v^{(l)}$  for layer l. The Update operation then combines the previous node embedding  $h_v^{(l-1)}$ with  $a_v^{(l)}$  to produce an updated embedding vector  $h_v^{(l)}$ . This updated embedding captures the properties of the node v itself and also the properties of its neighborhood N(v). The final propagated node embeddings after L iterations are denoted using the matrix  $\mathbf{H}^L$ . GNN implementations differ based on the employed Aggregate and Update functions. In our work, we consider the standard graph convolutional neural network (GCN) [41] and the graph isomorphism network (GIN) [52]. Their implementations are explained next, starting with the GCN.

**GCN:** In each iteration l, the embedding matrix  $\mathbf{H}^{(l)}$  will be updated as follows;

$$\mathbf{H}^{(l)} = \sigma(\widehat{\mathbf{D}}^{-\frac{1}{2}}\widehat{\mathbf{A}}\widehat{\mathbf{D}}^{-\frac{1}{2}}\mathbf{H}^{(l-1)}\mathbf{W}^{(l-1)})$$

(3)

The matrix  $\widehat{\mathbf{A}}$  is obtained by adding the identity matrix  $\mathbf{I}$  to the original adjacency matrix  $\mathbf{A}$ . This addition of selfloops enables the incorporation of the previously computed embeddings of the target nodes. The matrix  $\widehat{\mathbf{D}}$  is a diagonal degree matrix used for normalizing  $\widehat{\mathbf{A}}$ . The activation function  $\sigma(.)$  represents a non-linear activation function, such as the rectified linear unit (ReLU). The matrix  $\mathbf{W}^{(l-1)}$  is a trainable weight matrix.

**Graph Classification:** In order to perform graph classification, an overall graph-level embedding must be extracted by applying an order invariant READOUT function, such as Sum, Max, or Average, on the node embeddings  $\mathbf{H}^{(L)}$ . We denote the graph embedding for each graph G as  $h_G$ , which is used to make a prediction  $\hat{y}_G$  using a multilayer-perceptron (MLP) stage about the graph. For example, the GNN can be trained to minimize the cross-entropy loss for training graphs, as follows. Where  $y_G$  denotes the ground truth label.

$$Loss(\{y_G\}, \{\hat{y}_G\}) = \sum_G y_G * log_e(\hat{y}_G),$$

(4)

A common practice involves the addition of a pooling layer preceding the graph READOUT stage. This step focuses on selecting a subset of nodes for graph representation, as opposed to the simultaneous processing of all nodes. Specifically, in an Attention-based pooling layer, the top-k filtering technique can be applied based on the nodes' Attention scores. This procedure entails identifying and retaining the top-k nodes with the highest scores while discarding the rest.

To obtain the scores for the filtering process, one approach is to employ a separate trainable GNN layer that takes into account both the node features and the topological characteristics, as done in [51], [25].

GIN: The GIN updates node representations as follows.

Fig. 4. Proposed MaliGNNoma methodology: Synthesized netlists are transformed into DFGs for training a GNN to separate malicious and benign samples. A GNN explanation tool identifies nodes contributing to malicious classification.

$$h_v^{(l)} = \text{MLP}^{(l)} \left( h_v^{(l-1)} + \sum_{u \in N(v)} h_u^{(l-1)} \right)$$

(5)

GIN considers all structural information from all iterations of the model by concatenating graph embeddings across all layers of GIN as follows. The READOUT function adds all node embeddings from the same layer.

$$h_{G} = \text{CONCAT}\left(\text{READOUT}\left(\left\{h_{v}^{(l)}|v \in G\right\}\right) \mid l = 0, 1, \dots, L\right)$$

(6)

3) GNN Explanation: As with most neural networks, the process through which GNNs reach their classifications lacks a straightforward explanation for human understanding. Addressing this challenge, the authors in [53] introduced GN-NExplainer that implements an optimization task aimed at maximizing the mutual information between a GNN's prediction and a distribution of potential subgraph structures. Hence, GNNExplainer can identify the specific subgraph and node structures contributing to a particular classification. Expanding upon the concepts introduced in [53], D. Luo et al. have extended GNNExplainer and introduced PGExplainer [28]. PGExplainer is a versatile parameterized explainer designed to be applicable to a broad spectrum of GNN-based models. PGExplainer adopts a deep neural network to parameterize the generation process of explanations. Compared to existing work, PGExplainer exhibits superior generalization capabilities. Similar to GNNExplainer, PGExplainer provides a subgraph that influenced the GNN's prediction.

The quality of an explanation can be assessed using various metrics. One of the most common evaluation metric is fidelity-(detailed in [54]). Fidelity- evaluates the contribution of the generated explanatory subgraph to the initial prediction, by presenting only the subgraph to the model.

## III. PROPOSED MALIGNNOMA METHODOLOGY

In this section, we discuss our proposed MaliGNNoma framework in detail, as illustrated in Fig. 4. MaliGNNoma takes a post-synthesis netlist as input and converts it into a graph representation, effectively transforming the problem of identifying malicious circuits into a graph classification task. Additionally, it provides a list of influential nodes in the graph contributing to the prediction of a "*malicious*" label. Next, we discuss the netlist to graph conversion and the GNN learning steps. Subsequently, we will present the dataset generation process, which significantly impacts the success of the task.

# A. MaliGNNoma Pipeline

1) Netlist to DFG: MaliGNNoma employs the open-source PyVerilog tool to parse the Verilog netlists and convert them into DFGs (see Fig. 4 **1**), as explained in Section II-C1. MaliGNNoma assigns a one-hot encoded feature to each node in the DFG to indicate its type. The feature vector length per node is 37, representing all possible types of nodes in a DFG. X represents the nodes feature matrix.

2) GNN-based Learning: The graph G is passed through the employed graph-based learning pipeline, which consists of graph convolution layers, graph pooling layers, and graph READOUT (see Fig. 4 2). In our evaluation, we consider both the GCN and the GIN architectures explained in Section II-C2.

3) Localizing the Malicious Nodes: By utilizing the PG-Explainer, our model can identify the influential nodes contributing to the prediction of a "malicious" label.

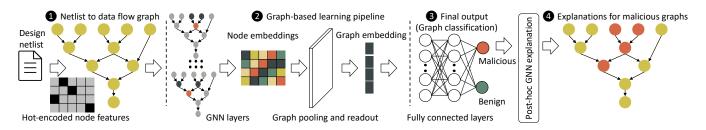

Fig. 5 1 showcases a high-level implementation of a fulladder with a MUX-based RO connection. The benign fulladder's DFG is depicted in 2 and classified as benign by MaliGNNoma. In contrast, (3) represents the DFG of the malicious full-adder with the MUX-based RO connection, classified as malicious by MaliGNNoma. Notably, MaliGNNoma goes beyond classification and highlights the most influential nodes (colored in red), corresponding to the MUX-based RO. This automated process aids in analyzing netlists and identifying malicious components, even in cases involving third-party IPs incorporated into the design. Please note that if a design has only one RO (such as this adder example), it will not lead to fault injection. However, MaliGNNoma will flag it, following the industry standard set by Xilinx and AWS tools. We aim to maintain a similarly strict policy. Yet, MaliGNNoma can be retrained to take into account the number of ROs when making the final decision, if required.

# B. Dataset Generation

We utilize a Xilinx UltraScale+ XCZU9EG FPGA contained on the ZCU102 board. We generate multiple bitstreams to configure the FPGA board with tenant designs. To replicate a multi-tenancy scenario, we employed 20 distinct reconfigurable regions within the FPGA. These regions vary in size, ranging from 50% of the FPGA resources (with room for an additional equally-sized tenant) to 15% of the FPGA resources (allowing space for up to five other equally-sized tenants).

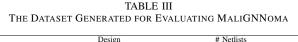

Based on these tenant regions, we built a dataset of 115 netlists. The netlists are based on benign designs from the

Fig. 5. Example of malicious full-adder with a MUX-based RO connected to its input. 2 The DFG of a benign full-adder without the MUX-based RO. The DFG with the MUX-based RO included. Also illustrates the output of the GNN explainer, highlighting the malicious nodes in the DFG, which correspond to the MUX-based RO.

ISCAS, Groundhog, Berkley, and OpenCores benchmarks in addition to a benign AES implementation to compare how well it can be differentiated from the maliciously modified AES. The netlists contain malicious designs as well, such as the MUX-based and Latch-based ROs as explained in [18], and advanced encryption standard (AES)-based attacks detailed in [21]. Moreover, we build attacks based on data encryption standard (DES) and secure hash algorithm (SHA) in a method similar to the AES-based attacks. For the AES-based attacks, we hide them with circuits from the ISCAS benchmark as explained in [23] to check how hard it is to detect them.

Table III shows the designs used and their numbers; overall we have 68 malicious designs and 47 benign designs. It should be noted that for the benign modules, it is not the same design repeated several times but rather several designs from the same benchmark, e.g., artificial neural network and bitcoin miner from OpenCores. It is worth noting that not all designs were compatible with every reconfigurable region due to resource limitations. Therefore, some designs were omitted from specific tenant regions if they could not fit within the assigned resources. This is not unreasonable as in real multitenant scenarios some tenant designs would not be able to use the smaller cheaper tenants regions.

Through these dataset generation techniques, we aimed to capture a wide range of realistic scenarios, considering resource constraints, design modifications, and potential attack

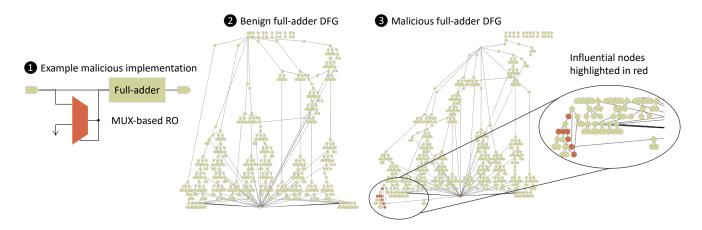

Fig. 6. MaliGNNoma graph embeddings for benign and malicious samples. The figure visually represents the 2-D T-SNE projection of the generated embeddings by MaliGNNoma for each graph. This visualization illustrates the optimized embedding generation, specifically tailored to separate malicious from benign circuits.

concealment, enabling comprehensive evaluation of our GNNbased malicious netlist classifier for secure cloud FPGAs.

# C. MaliGNNoma Integration

The MaliGNNoma pipeline may initially appear independent of the FPGA netlist scanning task. However, due to the trainable weights involved in the message passing step of the GNN, the MaliGNNoma procedure becomes optimized through training on the dataset comprising malicious and benign modules. Consequently, MaliGNNoma becomes specifically tailored to effectively differentiate between malicious and benign modules by mapping the graphs in an optimal manner. To visually demonstrate the effectiveness of MaliGNNoma in extracting meaningful representations from netlists, we utilize t-distributed stochastic neighbor embedding (t-SNE) [56] to map the GNN-generated embeddings of the dataset samples (discussed in Section III-B) onto a two-dimensional space.

The resulting visualization in Fig. 6 shows distinct clusters for malicious and benign samples, with no overlap, allowing for accurate classification. This highlights the optimization of the GNN stage to enhance the separation between malicious and benign FPGA netlists.

Fig. 7. MaliGNNoma experimental setup and tool flow.

## IV. EVALUATION

We summarize the experimental setup and the process of MaliGNNoma training in Fig 7. Next, we describe the experimental setup in detail.

# A. Experimental Setup

1) Evaluation Metrics: We report the classification Accuracy, Precision, Recall, and F1 score, calculated as follows

$$Prec. = \frac{TP}{TP + FP}, Recall = \frac{TP}{TP + FN}, F_1 = \frac{2 \times Prec. \times Recall}{Prec. + Recall}$$

(7)

TP and FP denote true positives and false positives. Accuracy measures the percentage of correctly classified samples.

For evaluating the GNN explanation, we utilize the fidelitymetric. Fidelity assesses the impact of the generated explanatory subgraph  $G_S$  on the original prediction  $\hat{y}$ . This can be evaluated by providing only the subgraph to the model (fidelity-). Fidelity measures the extent to which an explainable model accurately replicates the underlying natural phenomenon or the logic of the GNN model. The metric is calculated as follows, where D indicates the number of testing samples,  $y_i$  indicates the ground truth for sample i, and  $\hat{y}_i^{G_S}$ indicates the model's prediction for  $G_S$ :

$$\text{fid}_{-} = \frac{1}{D} \sum_{i=1}^{D} \left\| \mathscr{W}(\hat{y}_{i} = y_{i}) - \mathscr{W}(\hat{y}_{i}^{G_{S}} = y_{i}) \right\|$$

(8)

If represents the indicator function that takes on the value 1 when a certain condition is true and 0 when the condition is false. A sufficient explanation has a fidelity- score close to 0.

2) GNN Parameters: Since GNNs have not been previously applied to FPGA netlist analysis, in our experimental investigation, we explore two different GNN baselines, specifically the GIN and GCN, across various GNN configurations to assess their effectiveness.

For the GCN, we consider a baseline GCN with 2 to 3 layers and hidden dimensions of 100, 200, and 400. We also experiment with different *dropout* rates in the range of 0.1, 0.2, and 0.5,<sup>4</sup> after every GNN layer, along with the addition of an

attention pooling layer with pooling ratios of 20%, 50%, and 80%. Additionally, we explore different READOUT functions, including Max, Mean, and Sum.

For the GIN, we consider 2 and 3 layers with hidden dimensions of 64, 100, and 128. The default setup for the GIN employs a Sum READOUT function without a pooling layer. We add a dropout stage after the linear layer.

All models were trained for 100 epochs using the minibatch gradient descent algorithm with a batch size of 4 and a learning rate of 0.001.

3) Validation: For each sample in the dataset, a leaveone-out cross-validation approach is applied. The dataset is randomly shuffled, and for each sample, it is divided into a training set and a validation set (with a 10% split of the remaining data). During training, the GNN is evaluated on the validation set every 10 epochs. The GNN parameters that yield the best performance on the validation set are selected as the final model for testing. This process is carried out once for each sample in the dataset, with one sample left out for testing in each iteration.

# B. Results

1) Classification Performance: The best MaliGNNoma performance was achieved using 2 layers of GIN with a hidden dimension of 100 and a dropout rate of 0.5. This resulted in an accuracy of 98.24%, precision of 97.88%, recall of 98.5%, and an F1 score of 98.19%. MaliGNNoma effectively detects malicious netlist configurations, even sophisticated ones like AES-based, and achieves state-of-the-art performance in all aspects. Table IV presents the classification performance of MaliGNNoma on the various subsets of the dataset. As evident from the table, there were only two misclassifications in the entire dataset: one benign AES was misclassified as malicious, and one Latch-RO circuit was misclassified as benign.

2) Comparison of GNN Architectures: Comparing GCN to GIN, with the same hidden dimension of 100, GCN (with Max READOUT) achieves similar performance, with an accuracy of 94.73%. However, to achieve this result, a pooling ratio of 20% was applied, which was unnecessary for GIN. Overall, when comparing both, GIN exhibits greater expressiveness as it incorporates a neural network in the aggregation step, enabling it to capture more intricate relationships in the graph data. However, for both architectures, increasing the number of

<sup>&</sup>lt;sup>4</sup>Dropout is a regularization technique used to prevent overfitting in neural networks by randomly dropping out (setting to zero) some of the units in a layer during training.

TABLE IV MALIGNNOMA CLASSIFICATION RESULTS

|           | Design              | # Netlists Correctly Classified/Total # |  |  |

|-----------|---------------------|-----------------------------------------|--|--|

| Malicious | Modified AES [21]   | 8/8                                     |  |  |

|           | Modified DES        | 14/14                                   |  |  |

|           | Modified SHA        | 9/9                                     |  |  |

|           | Hidden attacks [23] | 7/7                                     |  |  |

|           | Latch-RO [18]       | 8/9                                     |  |  |

|           | MUX-RO [18]         | 21/21                                   |  |  |

| Benign    | ISCAS [29]          | 9/9                                     |  |  |

|           | Groundhog [31]      | 10/10                                   |  |  |

|           | Berkley [30]        | 4/4                                     |  |  |

|           | OpenCores [32]      | 16/16                                   |  |  |

|           | AES [55]            | 7/8                                     |  |  |

layers to 3 leads to a significant reduction in performance. For instance, in the case of GIN, this increase resulted in a notable accuracy drop to 77.19%. This effect is commonly referred to as "over-smoothing." Over-smoothing occurs when nodes lose their discriminative power because they aggregate information from too many neighbors, making them nearly identical.

3) GNN Explanation: After model training and testing, the model is passed to the PGExplainer to extract an explanatory subgraph from the entire graph representation of the netlist. This step is particularly crucial, especially in cases where a malicious label is predicted, as it provides justification for the model's decision. To evaluate the performance of subgraph extraction without relying on node labeling to identify malicious components, we use the fidelity- metric. An explanation is considered sufficient if it independently leads to the initial prediction of the model. Since there may be other configurations in the graph that could also lead to the same prediction, it is possible to have multiple sufficient explanations for a single prediction. A sufficient explanation is characterized by a fidelity- score close to 0. For our dataset, the average fidelity- score obtained is 0.28, with a fidelity- score of 0 being observed for 70% of the samples. This indicates that in the majority of cases, the extracted explanations are effective in justifying the model's predictions.<sup>5</sup>

4) *Runtime:* MaliGNNoma runs on a single machine of 10 cores (2x Intel(R) Xeon(R) CPU E5-2680 v4@2.4GHz). On average, MaliGNNoma training process for 100 epochs, including dataset reading and conversion to graphs, takes approximately 6 hours. It is important to note that this is an offline procedure. Once MaliGNNoma is trained, the inference time for each prediction averages around 0.05 seconds.

5) Comparison to Related Works: As we show in Table I, not all attack vectors are detected by the state-of-the-art. To quantify this, we compare MaliGNNoma against them based on our dataset. Table V shows the results of this comparison. As these tools are not openly available, we perform a conser-

TABLE V

Comparison to Related Work based on the Type of Attacks

They Mention they are Capable of Detecting. The comparison

Is conservative, giving them 100% accuracy in detecting the

Attacks mentioned in their works.

|          | Tool    | Tool    | Tool    | Tool    | Tool   | MaliGNN- |

|----------|---------|---------|---------|---------|--------|----------|

|          | of [23] | of [22] | of [19] | of [18] | of [8] | oma      |

| Accuracy | 80%     | 66.9%   | 86.1%   | 66.9%   | 66.9%  | 98.24%   |

vative comparison, i.e., we assume they have 100% accuracy in detecting the attacks they report capable of detecting. This is to their benefit, as realistically they have lower accuracy e.g., as reported in [23], [22], [19]. Even with this conservative comparison, MaliGNNoma outperforms all the state-of-theart solutions. The highest accuracy is theoretically reached by the tool of [23] which is still lower than the actual accuracy MaliGNNoma reaches.

# C. Discussion

1) Netlist Versus Bitstream: There may be concerns about processing the netlist instead of the bitstream due to potential piracy issues. However, it is important to note that a bitstream is not inherently secure and can be reverse-engineered [20]. Providing the netlist instead of the bitstream does not introduce any additional threats in terms of security. Only encrypted bitstreams can provide security, but they cannot be analyzed since they are indistinguishable from random data. The topic of incorporating obfuscation mechanisms in the netlist to make reverse engineering more difficult is a separate research direction that is not directly related to our work. Alternative to obfuscation, to preserve the security of the bitstreams, [17] shows an attestation scheme including bitstream checking for cloud FPGAs through a trusted third party. This attestation scheme or similar FPGA attestation schemes can be used for the netlist checking for malicious attacks, but their implementation is out of the scope of this work.

2) Security of GNNs: Recent research highlights the vulnerability of GNNs themselves to *poisoning* and *backdoor* attacks, particularly when training is outsourced [57], [58]. To mitigate this threat, there is a growing focus on developing robust GNN implementations. MaliGNNoma offers explainability and the potential to detect backdoor attacks. However, the specific application of explainability mechanisms for detecting backdoor attacks in GNNs analyzing circuits has not yet been extensively explored.

# V. CONCLUSIONS

We introduce MaliGNNoma, a defense method based on graph neural networks (GNNs) designed to ensure the security of cloud field-programmable gate arrays (FPGAs), including, but not limited to, multi-tenancy scenarios. MaliGNNoma can be employed by a hypervisor to scan input netlists for potential malicious circuit implementations before FPGA configuration, serving as the initial security layer in a much-needed multitiered security system. Unlike other scanning methods, MaliGNNoma directly learns from netlists instead of bitstreams,

<sup>&</sup>lt;sup>5</sup>The output of the GNN explainer represents connectivity (edges) between circuit components, not a list of primitives. We align with the state-of-the-art in ML, reporting explainability performance through the fidelity metric. This metric assesses whether removing the detected subgraph from the original graph and retesting the model can alter predictions, which we believe is a meaningful evaluation. Our findings reveal that the reported nodes/edges may not necessarily form a cluster within the circuit, especially in AES-based attacks where the entire circuit contributes to the fault-injection attack.

enabling it to detect a wide range of attacks with high accuracy. Our work showcases the first application of GNNs for FPGA security. Further, we open-source MaliGNNoma.

#### ACKNOWLEDGMENTS

This work was partially funded by the "Helmholtz Pilot Program for Core Informatics (KiKIT)" at Karlsruhe Institute of Technology (KIT), and the German Federal Ministry of Education and Research (BMBF) through the Software Campus Project. Further, the work of Lilas Alrahis was supported by the KIT International Excellence Fellowship.

# REFERENCES

- C. Jin, V. Gohil, R. Karri, and J. Rajendran, "Security of cloud FPGAs: A survey," arXiv preprint arXiv:2005.04867, 2020.

- [2] Amazon Web Services (AWS). (2021) EC2 F1 instances. [Online]. Available: https://aws.amazon.com/ec2/instance-types/f1/

- [3] D. Rankin, J. Krupa, P. Harris, M. A. Flechas, B. Holzman, T. Klijnsma, K. Pedro, N. Tran, S. Hauck, S.-C. Hsu *et al.*, "FPGAs-as-a-service toolkit (FaaST)," in *IEEE/ACM International Workshop on Heterogeneous High-performance Reconfigurable Computing (H2RC)*. IEEE, 2020, pp. 38–47.

- [4] K. Eguro and R. Venkatesan, "Fpgas for trusted cloud computing," in 22nd International Conference on Field Programmable Logic and Applications (FPL), 2012, pp. 63–70.

- [5] D. R. E. Gnad, F. Oboril, and M. B. Tahoori, "Voltage drop-based fault attacks on FPGAs using valid bitstreams," in *Int. Conf. on FPL and Appl.*, 2017, pp. 1–7.

- [6] T. La, K. Pham, J. Powell, and D. Koch, "Denial-of-service on fpga-based cloud infrastructures — attack and defense," *IACR Transactions on Cryptographic Hardware and Embedded Systems*, vol. 2021, no. 3, p. 441–464, Jul. 2021. [Online]. Available: https://tches.iacr.org/index.php/TCHES/article/view/8982

- [7] A. Vaishnav, K. D. Pham, and D. Koch, "A survey on fpga virtualization," in *International Conference on Field Programmable Logic and Applications (FPL)*. IEEE, 2018, pp. 131–1317.

- [8] J. Krautter, D. R. E. Gnad, and M. B. Tahoori, "Mitigating electricallevel attacks towards secure multi-tenant FPGAs in the cloud," ACM *Transactions on Reconfigurable Technology and Systems*, vol. 12, no. 3, pp. 1–26, 2019.

- [9] F. Schellenberg, D. R. Gnad, A. Moradi, and M. B. Tahoori, "An inside job: Remote power analysis attacks on fpgas," in *Design, Automation* & *Test in Europe Conference & Exhibition (DATE)*. IEEE, 2018, pp. 1111–1116.

- [10] C. Ramesh, S. B. Patil, S. N. Dhanuskodi, G. Provelengios, S. Pillement, D. Holcomb, and R. Tessier, "Fpga side channel attacks without physical access," in 2018 IEEE 26th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM). IEEE, 2018, pp. 45–52.

- [11] S. Moini, S. Tian, D. Holcomb, J. Szefer, and R. Tessier, "Remote power side-channel attacks on bnn accelerators in fpgas," in 2021 Design, Automation & Test in Europe Conference & Exhibition (DATE), 2021, pp. 1639–1644.

- [12] J. Krautter, D. R. E. Gnad, and M. B. Tahoori, "Remote fault attacks in multitenant cloud fpgas," *IEEE Design & Test*, vol. 39, no. 4, pp. 33–40, 2022.

- [13] —, "FPGAhammer: remote voltage fault attacks on shared FPGAs, suitable for DFA on AES," *IACR Trans. on Cryptographic HW and Embedded Sys. (TCHES)*, vol. 2018, no. 3, pp. 44–68, 2018.

- [14] A. Boutros, M. Hall, N. Papernot, and V. Betz, "Neighbors from hell: Voltage attacks against deep learning accelerators on multi-tenant fpgas," in *International Conference on Field-Programmable Technology* (*ICFPT*), 2020, pp. 103–111.

- [15] J. Krautter, D. R. Gnad, F. Schellenberg, A. Moradi, and M. B. Tahoori, "Active fences against voltage-based side channels in multi-tenant FP-GAs," in 2019 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2019, pp. 1–8.

- [16] M. M. Ahmadi, L. Alrahis, O. Sinanoglu, and M. Shafique, "FPGA-Patch: Mitigating remote side-channel attacks on fpgas using dynamic patch generation," in ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED), 2023.

- [17] S. Zeitouni, J. Vliegen, T. Frassetto, D. Koch, A.-R. Sadeghi, and N. Mentens, "Trusted configuration in cloud fpgas," in 2021 IEEE 29th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), 2021, pp. 233–241.

- [18] T. M. La, K. Matas, N. Grunchevski, K. D. Pham, and D. Koch, "FP-GADefender: Malicious self-oscillator scanning for Xilinx UltraScale+ FPGAs," ACM Transactions on Reconfigurable Technology and Systems (TRETS), vol. 13, no. 3, pp. 1–31, 2020.

- [19] J. Chaudhuri and K. Chakrabarty, "Diagnosis of malicious bitstreams in cloud computing fpgas," *IEEE Transactions on Computer-Aided Design* of Integrated Circuits and Systems, 2023.

- [20] K. Dang Pham, E. Horta, and D. Koch, "Bitman: A tool and api for fpga bitstream manipulations," in *Design, Automation & Test in Europe Conference & Exhibition (DATE), 2017*, 2017, pp. 894–897.

- [21] G. Provelengios, D. Holcomb, and R. Tessier, "Power wasting circuits for cloud FPGA attacks," in *Int. Conf. on Field-Prog. Logic and Appl.* (*FPL*), 2020, pp. 231–235.

- [22] J. Chaudhuri and K. Chakrabarty, "Detection of malicious fpga bitstreams using cnn-based learning," in 2022 IEEE European Test Symposium (ETS), 2022, pp. 1–2.

- [23] R. Elnaggar, J. Chaudhuri, R. Karri, and K. Chakrabarty, "Learning malicious circuits in fpga bitstreams," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 42, no. 3, pp. 726–739, 2023.

- [24] R. Yasaei, S.-Y. Yu, E. K. Naeini, and M. A. A. Faruque, "GNN4IP: Graph neural network for hardware intellectual property piracy detection," in 2021 58th ACM/IEEE Design Automation Conference (DAC), 2021, pp. 217–222.

- [25] L. Alrahis, A. Sengupta, J. Knechtel, S. Patnaik, H. Saleh, B. Mohammad, M. Al-Qutayri, and O. Sinanoglu, "GNN-RE: Graph neural networks for reverse engineering of gate-level netlists," *IEEE Transactions* on Computer-Aided Design of Integrated Circuits and Systems, vol. 41, no. 8, pp. 2435–2448, 2022.

- [26] T. Bücher, L. Alrahis, G. Paim, S. Bampi, O. Sinanoglu, and H. Amrouch, "AppGNN: Approximation-aware functional reverse engineering using graph neural networks," in 2022 IEEE/ACM International Conference On Computer Aided Design (ICCAD), 2022, pp. 1–9.

- [27] L. Alrahis, J. Knechtel, and O. Sinanoglu, "Graph neural networks: A powerful and versatile tool for advancing design, reliability, and security of ICs," in 2023 28th Asia and South Pacific Design Automation Conference (ASP-DAC), 2023, pp. 83–90.

- [28] D. Luo, W. Cheng, D. Xu, W. Yu, B. Zong, H. Chen, and X. Zhang, "Parameterized explainer for graph neural network," *Advances in neural information processing systems*, vol. 33, pp. 19620–19631, 2020.

- [29] F. Brglez, D. Bryan, and K. Kozminski, "Combinational profiles of sequential benchmark circuits," in *ISCAS*, 1989, pp. 1929–1934 vol.3.

- [30] J. Pistorius, M. Hutton, A. Mishchenko, and R. Brayton, "Benchmarking method and designs targeting logic synthesis for fpgas," in *Proc. IWLS*, vol. 7, 2007, pp. 230–237.

- [31] P. Jamieson, T. Becker, P. Y. K. Cheung, W. Luk, T. Rissa, and T. Pitkänen, "Benchmarking and evaluating reconfigurable architectures targeting the mobile domain," ACM Transactions on Design Automation of Electronic Systems (TODAES), vol. 15, no. 2, mar 2010.

- [32] OpenCores. (1999) Opencores the reference community for free and open source gateware ip cores. [Online]. Available: https://opencores.org

- [33] M. M. Alam, S. Tajik, F. Ganji, M. Tehranipoor, and D. Forte, "RAM-Jam: Remote temperature and voltage fault attack on FPGAs using memory collisions," in *Workshop on Fault Diagnosis and Tolerance in Cryptography (FDTC)*, 2019, pp. 48–55.

- [34] H. Salmani, M. Tehranipoor, S. Sutikno, and F. Wijitrisnanto, "Trust-Hub Trojan benchmark for hardware Trojan detection model creation using machine learning," 2022. [Online]. Available: https: //dx.doi.org/10.21227/px6s-sm21

- [35] M. Zhao and G. E. Suh, "Fpga-based remote power side-channel attacks," in 2018 IEEE Symposium on Security and Privacy (SP), 2018, pp. 229–244.

- [36] Y. Zhang, R. Yasaei, H. Chen, Z. Li, and M. A. Al Faruque, "Stealing neural network structure through remote fpga side-channel analysis," *IEEE Transactions on Information Forensics and Security*, vol. 16, pp. 4377–4388, 2021.

- [37] T. Sugawara, K. Sakiyama, S. Nashimoto, D. Suzuki, and T. Nagatsuka, "Oscillator without a combinatorial loop and its threat to FPGA in data centre," *Electronics Letters*, vol. 55, no. 11, pp. 640–642, 2019.

- [38] K. Matas, T. M. La, K. D. Pham, and D. Koch, "Power-hammering through glitch amplification – attacks and mitigation," in *FCCM*, 2020, pp. 65–69.

- [39] J. Krautter, D. R. Gnad, and M. B. Tahoori, "Remote and stealthy fault attacks on virtualized fpgas," in 2021 Design, Automation & Test in Europe Conference & Exhibition (DATE). IEEE, 2021, pp. 1632–1637.

- [40] H. Nassar, H. AlZughbi, D. Gnad, L. Bauer, M. Tahoori, and J. Henkel, "LoopBreaker: Disabling interconnects to mitigate voltage-based attacks in multi-tenant FPGAs," in *International Conference on Computer-Aided Design (ICCAD)*, 2021.

- [41] T. N. Kipf and M. Welling, "Semi-supervised classification with graph convolutional networks," in *International Conference on Learning Rep*resentations (ICLR), 2017.

- [42] L. Alrahis, S. Patnaik, M. Shafique, and O. Sinanoglu, "Embracing graph neural networks for hardware security," in 2022 IEEE/ACM International Conference On Computer Aided Design (ICCAD), 2022, pp. 1–9.

- [43] —, "OMLA: An oracle-less machine learning-based attack on logic locking," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 69, no. 3, pp. 1602–1606, 2022.

- [44] R. Yasaei, S.-Y. Yu, and M. A. Al Faruque, "GNN4TJ: Graph neural networks for hardware trojan detection at register transfer level," in 2021 Design, Automation & Test in Europe Conference & Exhibition (DATE), 2021, pp. 1504–1509.

- [45] L. Alrahis, S. Patnaik, M. Shafique, and O. Sinanoglu, "MuxLink: Circumventing learning-resilient mux-locking using graph neural networkbased link prediction," in 2022 Design, Automation & Test in Europe Conference & Exhibition (DATE), 2022, pp. 694–699.

- [46] L. Alrahis, S. Patnaik, M. A. Hanif, M. Shafique, and O. Sinanoglu, "UNTANGLE: Unlocking routing and logic obfuscation using graph neural networks-based link prediction," in 2021 IEEE/ACM International Conference On Computer Aided Design (ICCAD), 2021, pp. 1–9.

- [47] L. Alrahis, L. Mankali, S. Patnaik, A. Sengupta, J. Knechtel, and O. Sinanoglu, "UN-SPLIT: Attacking split manufacturing using link prediction in graph neural networks," in *International Conference on Security, Privacy, and Applied Cryptography Engineering.* Springer, 2023, pp. 197–213.

- [48] L. Mankali, L. Alrahis, S. Patnaik, J. Knechtel, and O. Sinanoglu, "Titan: Security analysis of large-scale hardware obfuscation using graph neural networks," *IEEE Transactions on Information Forensics and Security*, vol. 18, pp. 304–318, 2022.

- [49] L. Alrahis, J. Knechtel, F. Klemme, H. Amrouch, and O. Sinanoglu, "GNN4REL: Graph neural networks for predicting circuit reliability degradation," *IEEE Transactions on Computer-Aided Design of Inte*grated Circuits and Systems, vol. 41, no. 11, pp. 3826–3837, 2022.

- [50] D. S. Lopera, L. Servadei, G. N. Kiprit, S. Hazra, R. Wille, and W. Ecker, "A survey of graph neural networks for electronic design automation," in 2021 ACM/IEEE 3rd Workshop on Machine Learning for CAD (MLCAD), 2021, pp. 1–6.

- [51] S.-Y. Yu, R. Yasaei, Q. Zhou, T. Nguyen, and M. A. Al Faruque, "HW2VEC: a graph learning tool for automating hardware security," in 2021 IEEE International Symposium on Hardware Oriented Security and Trust (HOST), 2021, pp. 13–23.

- [52] K. Xu, W. Hu, J. Leskovec, and S. Jegelka, "How powerful are graph neural networks?" in *ICLR*, 2019.

- [53] Z. Ying, D. Bourgeois, J. You, M. Zitnik, and J. Leskovec, "Gnnexplainer: Generating explanations for graph neural networks," *Advances in neural information processing systems*, vol. 32, 2019.

- [54] K. Amara, R. Ying, Z. Zhang, Z. Han, Y. Shan, U. Brandes, S. Schemm, and C. Zhang, "Graphframex: Towards systematic evaluation of explainability methods for graph neural networks," *arXiv preprint arXiv:2206.09677*, 2022.

- [55] J. Strombergson, Verilog AES Core, Secworks Sweden AB, 2014.

- [56] L. V. D. Maaten and G. Hinton, "Visualizing data using t-sne," *Journal of machine learning research*, vol. 9, no. Nov, pp. 2579–2605, 2008.

- [57] L. Alrahis, S. Patnaik, M. A. Hanif, M. Shafique, and O. Sinanoglu, "PoisonedGNN: Backdoor attack on graph neural networks-based hardware security systems," *IEEE Transactions on Computers*, 2023.

- [58] L. Alrahis and O. Sinanoglu, "Graph neural networks for hardware vulnerability analysis—can you trust your GNN?" in *IEEE VLSI Test Symposium (VTS)*, 2023, pp. 1–4.