# **RowPress Vulnerability in Modern DRAM Chips**

Haocong Luo<sup>§</sup> Ataberk Olgun<sup>§</sup> A. Giray Yağlıkçı<sup>§</sup> Yahya Can Tuğrul<sup>§</sup> Steve Rhyner<sup>§</sup>

Meryem Banu Cavlak<sup>§</sup> Joël Lindegger<sup>§</sup> Mohammad Sadrosadati<sup>§</sup> Onur Mutlu<sup>§</sup>

§ETH Zürich

Memory isolation is a critical property for system reliability, security, and safety. We demonstrate RowPress, a DRAM read disturbance phenomenon different from the well-known RowHammer. RowPress induces bitflips by keeping a DRAM row open for a long period of time instead of repeatedly opening and closing the row. We experimentally characterize RowPress bitflips, showing their widespread existence in commodity offthe-shelf DDR4 DRAM chips. We demonstrate RowPress bitflips in a real system that already has RowHammer protection, and propose effective mitigation techniques that protect DRAM against both RowHammer and RowPress.

#### 1. Motivation

To ensure system robustness (i.e., reliability, security, and safety), it is critical to maintain memory isolation: accessing a memory address should not cause unintended side-effects on data stored in other addresses. Unfortunately, with aggressive technology node scaling, dynamic random access memory (DRAM), the prevalent main memory technology, suffers from increased *read disturbance*: accessing (reading) a DRAM cell disturbs the operational characteristics (e.g., stored charge) of other physically close DRAM cells.

RowHammer [1] is an example read-disturb phenomenon where *repeatedly* opening and closing (i.e., hammering) a DRAM row (called aggressor row) *many times* (e.g., tens of thousands times) can cause *bitflips* in physically nearby rows (called victim rows). RowHammer is a critical security vulnerability as attackers can induce and exploit the bitflips to take over a system or leak private or security-critical data [2]. To ensure robust operation in modern and future DRAM-based systems, it is critical to develop a rigorous understanding of read disturbance effects like RowHammer.

# 2. RowPress

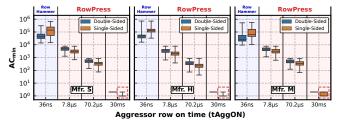

Our ISCA 2023 paper [3] experimentally demonstrates another widespread read-disturb phenomenon different from RowHammer, *RowPress*, in real commodity off-the-shelf DDR4 DRAM chips. We show that keeping a DRAM row (i.e., aggressor row) open for a long period of time (i.e., having a long aggressor row on time,  $t_{AggON}$ ) disturbs physically nearby DRAM rows. Doing so induces bitflips in the victim row *without* requiring (tens of) thousands of activations to the aggressor row like RowHammer. To illustrate this, Figure 1 shows the distribution of the minimum number of total aggressor row activations to cause at least one bitflip ( $AC_{min}$ ) of RowHammer and RowPress. Each box-and-whiskers represents the  $AC_{min}$  distribution (y-axis) when the aggressor DRAM row is open for  $t_{AggON}$  (x-axis) we measure in 164 commodity off-the-shelf DRAM chips from all three major DRAM manufacturers (i.e., Mfr. S, H, and M, corresponding to Samsung, SK Hynix, Micron; see Table 1). The box represents the the first (lower edge) and third (upper edge) quartile of the measured  $AC_{min}$  values, and the whiskers show the minimum and maximum values. The DRAM temperature is set to 80 °C (still within the "Normal Operating Temperature Range" as defined by the JEDEC DDR4 standard [4]).

Fig. 1:  $AC_{min}$  distributions of conventional RowHammer (RH) and three representative cases of RowPress (RP) at  $80^{\circ}C$  across 164 DDR4 chips from manufacturers S, H, and M.

The two leftmost boxes in each plot show the distribution of the minimum number of total aggressor row activations to cause at least one bitflip ( $AC_{min}$ ) for the conventional singlesided (orange) and double-sided (blue) RowHammer patterns, where the aggressor row is open for the minimum amount of time ( $t_{AggON} = t_{RAS} = 36 \text{ ns}$ ) allowed by the DRAM specification [4], as done in conventional RowHammer attacks. We observe that as  $t_{AggON}$  increases, compared to the most effective RowHammer pattern, the most effective RowPress pattern reduces  $AC_{min}$  1) by  $17.6 \times$  on average (up to  $40.7 \times$ ) when  $t_{AggON}$  is as large as the refresh interval ( $7.8 \,\mu$ s), 2) by  $159.4 \times$  on average (up to  $363.8 \times$ ) when  $t_{AggON}$  is  $70.2 \,\mu$ s, the maximum allowed  $t_{AggON}$  according to the current JEDEC standard [4], and 3) in extreme cases, down to *only one* activation (e.g., when  $t_{AggON} = 30 \,\text{ms}$ , highlighted by red boxes).

To our knowledge, our ISCA 2023 paper is the first work to experimentally demonstrate the RowPress phenomenon and its widespread existence in real commodity off-the-shelf DDR4 DRAM chips from all three major DRAM manufacturers. In this article, we 1) provide an extensive and rigorous real-device characterization of RowPress, demonstrating its unique characteristics that are different from RowHammer, 2) as a proof of concept, develop a *user-level* program that leverages RowPress to induce bitflips on a real system with DRAM that already has RowHammer protection, and 3) propose and evaluate a systematic methodology to adapt existing RowHammer mitigation techniques to *also* mitigate RowPress. Our results suggest that DRAM-based systems need to take RowPress into account to maintain the fundamental security/safety/reliability property of memory isolation and achieve robust operation. Based on our findings, we discuss and evaluate the implications of RowPress on existing read-disturb mitigation mechanisms that consider *only* RowHammer. To enable 1) reproduction and replication of our results, and 2) further research on RowPress, we open-source all our infrastructure, test programs, and data at https://github.com/CMU-SAFARI/RowPress. Extended results of our work and detailed analyses can be found in the arXiv version of our paper [5].

# 3. Real DRAM Chip Characterization

# 3.1. Characterization Methodology

**Infrastructure.** We characterize commodity DDR4 DRAM chips using an FPGA-based DRAM testing infrastructure based on DRAM Bender [6] that enables us fine-grained control of the DRAM commands, timings, and temperature of the DRAM chips. Figure 2 shows the four main components of our infrastructure: 1) a host machine that generates the characterization program and collects experiment results, 2) an FPGA development board that the memory module with the DRAM chips under characterization are connected to, programmed with DRAM Bender [6] that executes the characterization programs, 3) a thermocouple temperature sensor and a pair of heater pads pressed against the DRAM chips, and 4) a PID temperature controller that controls the heaters and maintains the temperature at the desired level.

Fig. 2: Our DDR4 DRAM testing infrastructure.

DRAM Chips Characterized. We characterize 164 real DDR4 DRAM chips from 21 commodity off-the-shelf DRAM modules (shown in Table 1). To demonstrate that RowPress is intrinsic to the DRAM technology and is a widespread phenomenon across manufacturers, we test a variety of DRAM chips spanning different die densities and die revisions from all three major DRAM chip manufacturers (Mfr. S, H, and M). Key Metric. We quantify DRAM's vulnerability to read disturbance by measuring the minimum number of total aggressor row activations to cause at least one bitflip ( $AC_{min}$ ). A lower  $AC_{min}$  value means the DRAM is more vulnerable to read disturbance because fewer aggressor row activations are needed to induce bitflips. For every DRAM module, we characterize  $AC_{min}$  for 3072 DRAM rows (the first, the middle, and the last 1024 rows in bank 1) and report the minimum  $AC_{min}$  value across five repetitions. To avoid bitflips due to retention failures, we bound the duration of the  $AC_{min}$  characterization routine strictly within the  $64 \,\mathrm{ms}$  refresh window of the JEDEC DDR4 standard [4].

Table 1: Tested DDR4 DRAM Chips.

| Mfr.                 | #DIMMs | #Chips | Density | Die Rev. | Org. | Date  |

|----------------------|--------|--------|---------|----------|------|-------|

| Mfr. S<br>(Samsung)  | 2      | 8      | 8Gb     | В        | x8   | 20-53 |

|                      | 1      | 8      | 8Gb     | С        | x8   | N/A   |

|                      | 3      | 8      | 8Gb     | D        | x8   | 21-10 |

|                      | 2      | 8      | 4Gb     | F        | x8   | N/A   |

| Mfr. H<br>(SK Hynix) | 1      | 8      | 4Gb     | А        | x8   | 19-46 |

|                      | 1      | 8      | 4Gb     | Х        | x8   | N/A   |

|                      | 2      | 8      | 16Gb    | А        | x8   | 20-51 |

|                      | 2      | 8      | 16Gb    | С        | x8   | 21-36 |

| Mfr. M<br>(Micron)   | 1      | 16     | 8Gb     | В        | x4   | N/A   |

|                      | 2      | 4      | 16Gb    | В        | x16  | 21-26 |

|                      | 1      | 16     | 16Gb    | Е        | x4   | 20-14 |

|                      | 2      | 4      | 16Gb    | Е        | x16  | 20-46 |

|                      | 1      | 4      | 16Gb    | F        | x16  | 21-50 |

### 3.2. Key Characterization Results

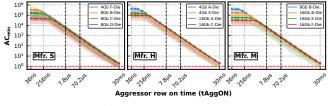

First, we characterize how RowPress amplifies DRAM's vulnerability to read disturbance by analyzing how  $AC_{min}$ changes as the aggressor row on time, t<sub>AggON</sub>, increases. We use a single-sided RowPress access pattern involving only one aggressor row, a fixed checkerboard data pattern (i.e., the aggressor row is initialized with 0xAA, and the victim rows are initialized with 0x55), and keep the DRAM temperature at  $50 \,^{\circ}\mathrm{C}$  (more access patterns, data patterns, and temperatures are examined in our ISCA 2023 paper [3] and its extended version [5]). Figure 3 shows the  $AC_{min}$  distribution (y-axis) of different die revisions for all three major DRAM manufacturers as we sweep  $t_{AggON}$  (x-axis) from 36 ns to  $30\,\mathrm{ms}$  in log-log scale. Note that when  $t_{\mathrm{AggON}}$  is  $36\,\mathrm{ns}$  (i.e., the left-most data points), the access pattern we characterize is identical to a conventional single-sided RowHammer pattern. For each manufacturer (i.e., each plot), we group the data based on the die revision (different colors) and then aggregate the  $AC_{min}$  values from all the rows we test. Each data point shows the mean  $AC_{min}$  value and the error band shows the minimum and maximum of  $AC_{min}$  values across all tested rows. We highlight the  $t_{AggON}$  values of 7.8 µs ( $t_{REFI}$ ) and  $70.2 \,\mu s \,(9 \times t_{REFI})$  on the x-axis, as they are the two potential upper bounds of  $t_{AggON}$ , as dictated by the JEDEC DDR4 standard [4]. We mark  $AC_{min} = 1 (10^{\circ})$  on the y-axis with dashed red lines.

Fig. 3: How  $AC_{min}$  changes as  $t_{AggON}$  increases.

We observe that across DRAM chips from all three manufacturers, 1)  $AC_{min}$  reduces by  $21 \times (190 \times)$  on average when  $t_{AggON}$  increases from 36 ns to 7.8 µs (70.2 µs), and 2) under extreme conditions (i.e., when  $t_{AggON} = 30$  ms), only a single aggressor row activation is enough to cause bitflips. Our results also show that DRAM chips with presumably more advanced technology nodes are more vulnerable to RowPress.

**Takeaway 1.** RowPress is a common read-disturb phenomenon in DRAM chips that exacerbates DRAM's vulnerability to read disturbance.

Second, we compare RowPress bitflips induced with  $AC_{min}$  (t<sub>AggON</sub> > 36 ns) to 1) RowHammer bitflips that are also induced at  $AC_{min}$  (t<sub>AggON</sub> = 36 ns), and 2) retention failure bitflips induced with an accelerated retention failure profiling methodology (i.e., we set the DRAM temperature to 80 °C, initialize the DRAM rows with the checkerboard data pattern, and disable auto-refresh for four seconds). Our results show that 1) an overwhelming majority of RowPress bitflips are different from those caused by RowHammer and retention failures, and 2) RowPress and RowHammer bitflips have *opposite* directions. For example, 1) for  $t_{AggON} \ge 7.8 \, \mu s$ , on average, only less than 0.013% of DRAM cells vulnerable to RowPress overlap with those vulnerable to RowHammer, and less than 0.34% overlap with retention failures, and 2) the majority of RowHammer bitflips in the DRAM chips we characterize are from logical "0" to logical "1" while the majority of RowPress bitflips are from logical "1" to logical "0" (note that logical bit values do not always correspond to physical charge levels stored in the DRAM cell [7]). These results suggest that different failure mechanisms lead to RowPress and RowHammer bitflips.

**Takeaway 2.** RowPress has a different failure mechanism from RowHammer and data retention failures in DRAM. There is almost no overlap between RowPress, RowHammer, and data retention bitflips, and the directionality of RowHammer and RowPress bitflips show opposite trends.

Third, we study the sensitivity of RowPress bitflips with respect to the change in temperature and access pattern. We observe that at a higher temperature of  $80 \degree$ C, RowPress reduces  $AC_{min}$  even more compared to  $50 \degree$ C. For example, when  $t_{AggON}$  is 7.8 µs, the average  $AC_{min}$  at  $80 \degree$ C is only  $0.55 \times$ ,  $0.32 \times$ , and  $0.59 \times$  of that at  $50 \degree$ C, for Mfr. S, H, and M, respectively.

**Takeaway 3.** RowPress gets significantly worse as temperature increases. This behavior is very different from how RowHammer bitflips change with temperature (as shown in two prior works, [1] and [8]).

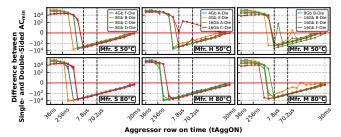

Fourth, we compare the  $AC_{min}$  values of the single-sided RowPress pattern involving only a single aggressor row to the double-sided RowPress pattern where two aggressor rows sandwiching a victim row are activated alternatingly. Figure 4 shows the difference between single- and double-sided  $AC_{min}$  (i.e.,  $AC_{min}(single) - AC_{min}(double)$ ) at  $50^{\circ}C$  (first row) and  $80^{\circ}C$  (second row).

We observe that as  $t_{AggON}$  increases, at both 50 °C and 80 °C, the  $AC_{min}$  of single-sided RowPress is initially larger than that of double-sided RowPress. However, as  $t_{AggON}$  continues to increase, the  $AC_{min}$  of single-sided RowPress becomes *smaller* than that of double-sided RowPress (i.e., single-

Fig. 4: Single-sided  $AC_{min}$  minus double-sided  $AC_{min}$  at  $50^{\circ}C$  (first row) and  $80^{\circ}C$  (second row).

sided RowPress becomes more effective at inducing bitflips because it needs *less* aggressor row activations).

**Takeaway 4.** RowPress behaves very differently from RowHammer as we change the access pattern from singlesided to double-sided. As  $t_{AggON}$  increases beyond a certain value, RowPress needs fewer aggressor row activations to induce bitflips with the single-sided pattern compared to the double-sided pattern.

We do not fully understand the underlying reasons for the observed phenomena and the low-level failure mechanisms of RowPress. We call for more future work in this direction to build a more comprehensive understanding of RowPress and read disturbance in DRAM in general.

Our ISCA 2023 paper [3] and its extended version [5] provide more comprehensive real-device characterization results and more detailed analyses, including the fraction of DRAM rows vulnerable to RowPress, RowPress bitflips' sensitivity to different data patterns, the minimum  $t_{AggON}$  to induce at least one bitflip for a fixed aggressor row activation count, a more fine-grained temperature study, the effect of increased aggressor row off time ( $t_{AggOFF}$ ), and the repeatability of RowPress bitflips.

# 4. Proof-of-Concept Real System Demonstration

## 4.1. Methodology

We demonstrate that an unprivileged *user-level* program can induce RowPress bitflips in a real system that uses DDR4 main memory and already has RowHammer protection. The system we evaluate consists of an Intel Core i5-10400 (Comet Lake) processor and a DDR4 DRAM module from Mfr. S with 8Gb C-Die DRAM chips. The DRAM chips on this module has Target Row Refresh (TRR) [9], a widely adopted in-DRAM RowHammer mitigation mechanism [10] employed by DRAM manufacturers.

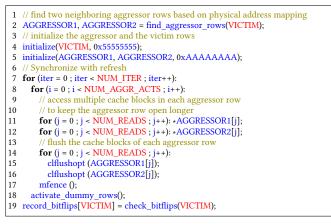

### 4.2. Demonstration Program

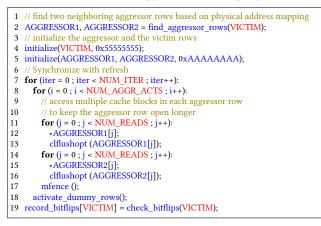

Algorithm 1 shows the key part of our RowPress demonstration program. The program repeatedly 1) accesses *multiple* (i.e., NUM\_READS) cache blocks in *the same aggressor DRAM row* (line 11 and 12) so that the memory controller keeps the aggressor row open for a longer period of time to better serve these accesses, and 2) flushes the accessed cache blocks from the cache (lines 14-16) so that future accesses will activate the aggressor row in DRAM. Note that when NUM\_READS is 1, the program is identical to a conventional RowHammer program.

Algorithm 1: RowPress demonstration program.

In the extended version of our paper [5], we investigate the effect of changing the *program order* of the accesses and cache flushes to the cache blocks in the aggressor row (lines 11-16 in Algorithm 2). In Algorithm 2, every access to a cache block in the aggressor row is immediately followed by a clflushopt instruction (in program order), unlike in Algorithm 1 where all the clflushopt instructions are after all the accesses to the cache blocks in the aggressor row (in program order).

Algorithm 2: RowPress demonstration program with a different program order of accesses to and flushes of cache blocks in the aggressor row.

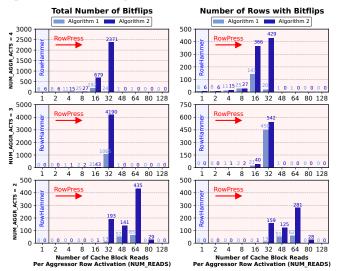

We run both programs on our evaluated real system using 1500 arbitrarily selected victim rows. Figure 5 shows the total number of bitflips we observe (left) and the number of rows with bitflips (right) using both Algorithm 1 (light blue bars) and Algorithm 2 (dark blue bars). The top, middle, and bottom plots show the numbers of accesses to the aggressor row per iteration being 4, 3, and 2, respectively (i.e., NUM\_AGGR\_ACT = 4,3,2). The x-axis shows the numbers of cache blocks read for every access to the aggressor row (i.e., NUM\_READS). The

leftmost bar in each graph shows the number of *conventional RowHammer-induced* bitflips, where we read *only a single* cache block per aggressor row activation (i.e., NUM\_READS = 1), such that the aggressor row is kept open for a short time. Remaining bars in each graph show results for RowPress-induced bitflips (with an increasing number of cache block reads from left to right, such that the aggressor row is kept open for an increasing amount of time).

Fig. 5: Number of RowHammer vs. RowPress bitflips (left) and number of rows with bitflips (right) we observe after running our proof of concept test programs with Algorithm 1 (blue bars) and Algorithm 2 (purple bars) with four (top), three (middle), and two (bottom) activations per aggressor row per iteration.

We observe that 1) both programs induce bitflips much more effectively on the evaluated system by leveraging Row-Press compared to RowHammer, and 2) the access-flush program order in Algorithm 2 greatly increases the number of RowPress bitflips compared to Algorithm 1 (by up to 98.79×). For example, when NUM\_AGGR\_ACT=2 and 3, RowHammer (i.e., NUM\_READ=1) does *not* induce any bitflip, RowPress induces up to 4190 bitflips in 542 DRAM rows when NUM\_READ=32 and NUM\_AGGR\_ACT=3 (Algorithm 2). When NUM\_AGGR\_ACT=4, while RowHammer induces only 4 bitflips in only 4 DRAM rows, RowPress induces up to 2371 bitflips in 429 DRAM rows (NUM\_READ=32, Algorithm 2).

**Takeaway 5.** A user-level program is much more effective at inducing bitflips on a real system by leveraging RowPress compared to RowHammer.

# 5. Mitigating RowPress

Our characterization results and proof-of-concept real system demonstration suggest that DRAM-based systems need to take RowPress into account to maintain the fundamental security/safety/reliability property of memory isolation and achieve robust operation. Based on our findings, we discuss and evaluate the implications of RowPress on existing read-disturb mitigation mechanisms that consider *only* RowHammer. We propose a methodology to adapt RowHammer mitigation techniques to also mitigate RowPress with low *additional* performance overhead by both 1) limiting the *maximum row-open time*, and 2) configuring the RowHammer defense to account for the RowPress-induced reduction in  $AC_{min}$ . By applying this methodology, our adapted mitigation techniques 1) still mitigate RowHammer because it is more aggressive at mitigating RowHammer than the original mitigation, and 2) also mitigate RowPress because the limited maximum row-open time bounds the reduction in  $AC_{min}$  that the mitigation technique needs to keep track of.

Using Ramulator [11], a cycle-accurate DRAM simulator, we experimentally demonstrate that by applying our proposed methodology to two major prior techniques (PARA [1] and Graphene [12]), we can mitigate both RowHammer and RowPress with an average (maximum) *additional* slowdown of only 3.6% (13.1%) and -0.63% (4.6%), respectively.The reason for the small negative slowdowns (i.e., speedups) is that limiting the maximum row open time improve fairness between cores in a way that increases weighted speedups. Our ISCA 2023 paper [3] and its extended version [5] 1) provide a more detailed evaluation and analysis of our proposed methodology, and 2) examine and discuss three other potential mitigations techniques for RowPress.

#### 6. Practical Industry Impact

We believe that our results, observations, and takeaways from our comprehensive real-device characterization, real system demonstration, and proposed mitigation of RowPress are critical for the industry to design fundamentally safe, secure, and reliable DRAM-based memory systems. RowPress opens up new a new attack surface on the memory system that could compromise the system, posing new challenges to DRAM manufacturers and system designers. We believe that existing read disturbance mitigation techniques that only consider RowHammer need to be adapted to also mitigate RowPress. System designers need to re-examine adaptive row buffer management policies in the memory controller to prevent them from being abused to conduct RowPress attacks. Future DRAM standards should also formalize and incorporate a DRAM chip's vulnerability to RowPress. Our work has received extensive media coverage [13] and was discussed heavily among technologists and industry professionals [14].

# 7. Research Impact

We believe that our paper can inspire and enable researchers across the computing stack. Some example directions include 1) craft new attacks that leverages RowPress to break memory isolation, 2) design new mitigation techniques that better protects DRAM from read disturbance at low cost, and 3) investigate the silicon-level mechanisms of RowPress to build a more comprehensive and fundamental understanding of read disturbance phenomenon in DRAM. Our paper clearly shows that further research is necessary for building fundamentally safe, secure, and reliable DRAM-based memory systems. We believe and hope that our novel results, observations, and takeaways will inspire future research in both academia and industry for crafting more effective readdisturb attacks and designing more effective and efficient mitigation techniques.

### 8. Author Biography

Haocong Luo is a Ph.D student at the SAFARI research group, ETH Zurich, advised by Prof. Onur Mutlu. His current research interest is in computer architecture, focusing on the performance and robustness of memory systems. He obtained MSc. in Computer Science from ETH Zurich, and BEng. in Computer Science from ShanghaiTech University. **Contact email address:** richardluo723@gmail.com

Ataberk Olgun is a Ph.D student at ETH Zürich, Zürich, Switzerland. Olgun received his master's degree in Computer Engineering from TOBB University of Economics and Technology. His research interests lie primarily in the area of Computer Architecture. In particular, his research interests include power-efficient and high-performance memory systems, and hardware security. **Contact email address:** olgunataberk@gmail.com

Yahya Can Tugrul received the bachelor's degree in electrics and electronics engineering from Middle East Technical University, Ankara, Türkiye, in 2020. He is currently pursuing the master's degree in computer engineering with the TOBB University of Economics and Technology, Ankara. He is a Scientific Assistant with ETH Zurich, Zürich, Switzerland. His research interests include secure and reliable DRAM architectures. Contact email address: yahyacantugrul@gmail.com

**Steve Rhyner** is a Computer Science MSc student at ETH Zurich. He holds a Bachelor of Science ETH in Computer Science degree from ETH Zurich. His research interests span Machine Learning, Artificial Intelligence, Data Science, and their intersection with Computer Architecture. He is a member of the SAFARI research group. **Contact email address:** steverhyner7@gmail.com

**Abdullah Giray Yağlıkçı** recently defended his PhD thesis, advised by Prof. Onur Mutlu. His current broader research interests are in computer architecture and hardware security, with a special focus on DRAM robustness and performance. In particular, his PhD research focuses on understanding and solving DRAM read disturbance vulnerability. Giray has published several works on this topic in major venues such as HPCA, MICRO, ISCA, USENIX Security, DSN, and SIGMET-RICS. Among these works, BlockHammer was named as a finalist by Intel in 2022 for the Intel Hardware Security Academic Award, Svärd received the first place in the ACM SRC at PACT 2023, and his dissertation was selected as one of the five finalists in the HOST 2024 PhD dissertation competition. Giray's RowHammer research is in part supported by Google Security and Privacy Research Award and the Microsoft Swiss Joint Research Center. **Contact email address:** giray.yaglikci@safari.ethz.ch

**Joël Lindegger** is a Ph.D student at the SAFARI research group, ETH Zürich. He received his master's degree in Computer Science from ETH Zürich. His research interests lie primarily in the area of accelerating genome analysis with software and hardware approaches. **Contact email address:** jmlindegger@gmail.com

Meryem Banu Cavlak received her bachelor's degree in Computer Engineering from Bilkent University, Ankara, Türkiye in 2021, and master's degree in Electrical Engineering and Information Technology from ETH Zürich, Zürich, Switzerland in 2024. Her research interests include bioinformatics and computer architecture. Contact email address: mbanucavlak@gmail.com

**Mohammad Sadrosadati** is a senior researcher and lecturer at SAFARI Research Group, ETH Zurich, working under the supervision of Prof. Onur Mutlu. His research interests are in near-data processing, memory/storage systems, heterogeneous computing, and interconnection networks. He received the B.Sc., M.Sc., and Ph.D. degrees in Computer Engineering from Sharif University of Technology, Tehran, Iran, in 2012, 2014, and 2019, respectively. **Contact email address:** m.sadr89@gmail.com

Onur Mutlu is a Professor of Computer Science at ETH Zurich. He is also a faculty member at Carnegie Mellon University, where he previously held the Strecker Early Career Professorship. His research interests are in computer architecture, systems, hardware security, bioinformatics. A variety of techniques he, along with his group and collaborators, has invented over the years have influenced industry and are employed in commercial microprocessors and memory/storage systems. He started the Computer Architecture Group at Microsoft Research (2006-2009), and held various product and research positions at Intel Corporation, AMD, VMware, and Google. He is an ACM Fellow, IEEE Fellow, and an elected member of the Academy of Europe. His computer architecture and digital design course lectures are freely available (https://www.youtube.com/OnurMutluLectures). His research group makes a wide variety of software and hardware artifacts freely available online (https://safari.ethz. ch/). Contact email address: omutlu@gmail.com

# Acknowledgements

We thank the anonymous reviewers of ISCA 2023 and IEEE Micro Top Picks 2024 for feedback. We thank the SAFARI Research Group members for valuable feedback and the stimulating intellectual environment they provide. We acknowledge the generous gift funding provided by our industrial partners (especially Google, Huawei, Intel, Microsoft, VMware), which has been instrumental in enabling the research we have been conducting on read disturbance in DRAM in particular and memory systems in general. This work was in part supported by the a Google Security and Privacy Research Award and

#### the Microsoft Swiss Joint Research Center.

#### References

- Y. Kim et al., "Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors," in ISCA, 2014.

- [2] O. Mutlu et al., "RowHammer: A Retrospective," IEEE TCAD, 2019.

- [3] H. Luo et al., "RowPress: Amplifying Read Disturbance in Modern DRAM Chips," in ISCA, 2023.

- [4] JEDEC, JESD79-4C: DDR4 SDRAM Standard, 2020.

- [5] H. Luo et al., "RowPress: Amplifying Read Disturbance in Modern DRAM Chips," arXiv:2306.17061, 2023.

- [6] A. Olgun et al., "DRAM Bender: An Extensible and Versatile FPGA-based Infrastructure to Easily Test State-of-the-art DRAM Chips," IEEE TCAD, 2023.

- [7] J. Liu et al., "An Experimental Study of Data Retention Behavior in Modern DRAM Devices," in ISCA, 2013.

- [8] L. Orosa et al., "A Deeper Look into RowHammer's Sensitivities: Experimental Analysis of Real DRAM Chips and Implications on Future Attacks and Defenses," in MICRO, 2021.

- [9] H. Hassan et al., "Uncovering in-DRAM RowHammer Protection Mechanisms: A New Methodology, Custom RowHammer Patterns, and Implications," in MICRO, 2021.

- [10] P. Frigo et al., "TRRespass: Exploiting the Many Sides of Target Row Refresh," in S&P, 2020.

- [11] Y. Kim et al., "Ramulator: A Fast and Extensible DRAM Simulator," CAL, 2016.

- [12] Y. Park et al., "Graphene: Strong yet Lightweight Row Hammer Protection," in MICRO, 2020.

- [13] ARS Technica, "There's a new way to flip bits in DRAM, and it works against the latest defenses," https://arstechnica.com/security/2023/10/ theres-a-new-way-to-flip-bits-in-dram-and-it-works-against-the-latest-defenses/.

- [14] Real World Tech, "RowPress," https://www.realworldtech.com/forum/?threadid= 212524.

#### 9. Sidebar: Related Works on DRAM Bitflips

To our knowledge, our ISCA 2023 paper is the first work to experimentally demonstrate and characterize RowPress and its *widespread* existence commodity off-the-shelf DRAM chips. This sidebar gives an overview of the related works.

**Real Chip Characterization of RowHammer.** Two major prior works on experimental real DRAM chip characterization of RowHammer ([1] and [2]) do not study the effect of increasing  $t_{tAggON}$ . One recent RowHammer characterization work [8] and three device-level studies ([4], [5], and [6]) provide preliminary results on how increasing  $t_{AggON}$  by small amounts affects RowHammer bitflips. These works treat this phenomenon the same as RowHammer and do *not* identify and demonstrate a second DRAM read-disturb phenomenon that is *different* from RowHammer, while our paper clearly demonstrates the difference between RowHammer and Row-Press. We refer interested readers to two overview papers( [2] and [8]) for more comprehensive overviews of different kinds of works on RowHammer.

**One-Location Hammering.** A prior work on exploiting RowHammer [9] proposes a single-sided RowHammer technique called "One-Location Hammering" that "continuously re-opens the same DRAM row." However, it is unclear whether the bitflips this work observes are caused by increased  $t_{AggON}$  or conventional single-sided RowHammer.

**Perspective From Industry.** Two patents from Micron [10], and [11] very briefly mention a "RAS Clobber" effect similar to RowPress. However, they do *not* provide any evaluation, analysis or demonstration of this effect or clearly distinguish this effect from RowHammer. A paper from Samsung placed on arXiv [12] while our ISCA 2023 paper has been under review identifies a "Passing Gate Effect" similar to RowPress, but they do not provide any detailed explanations or real DRAM chip characterization results.

We call for future works to study both 1) the high-level implications of RowHammer and RowPress on designing robust computing systems, and 2) the low-level failure mechanisms of RowPress and DRAM read disturbance in general.

#### Sidebar: References

- [1] Y. Kim et al., "Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors," in ISCA, 2014.

- [2] J. S. Kim et al., "Revisiting RowHammer: An Experimental Analysis of Modern Devices and Mitigation Techniques," in ISCA, 2020.

- [3] L. Orosa et al., "A Deeper Look into RowHammer's Sensitivities: Experimental Analysis of Real DRAM Chips and Implications on Future Attacks and Defenses," in MICRO, 2021.

- [4] K. Park et al., "Experiments and Root Cause Analysis for Active-Precharge Hammering Fault in DDR3 SDRAM under 3xnm Technology," Microelectronics Reliability, 2016.

- [5] T. Yang *et al.*, "Trap-Assisted DRAM Row Hammer Effect," *EDL*, 2019.

[6] L. Zhou *et al.*, "Double-sided row hammer effect in sub-20 nm dram: Physical

- [7] D. Zhou et al., "Double statut on harmonic effect in ab 20 mechanism, key features and mitigation," in *IRPS*, 2023.

[7] O. Mutlu et al., "RowHammer: A Retrospective," *IEEE TCAD*, 2019.

- [8] O. Mutlu et al., "Fundamentally Understanding and Solving RowHammer," in ASP-DAC, 2023.

- [9] D. Gruss et al., "Another Flip in the Wall of Rowhammer Defenses," in S&P, 2018.

[10] Y. Ito et al., "Apparatus and Methods for Refreshing Memory," U.S. Patent 11062754B2, 2019.

- [11] G. D. Wolff, "Word Line Cache Mode," U.S. Patent 10366733B1, 2019.

- [12] S. Hong et al., "DSAC: Low-Cost Rowhammer Mitigation Using In-DRAM Stochastic and Approximate Counting Algorithm," arXiv:2302.03591, 2023.