# Efficient and Flexible Different-Radix Montgomery Modular Multiplication for Hardware **Implementation**

Yuxuan Zhang¹ ,Hua Guo(⊠)¹, Chen Chen¹, Yewei Guan¹, Xiyong Zhang²

and Zhenyu Guan<sup>1</sup>

School of Cyber Science and Technology, Beihang University, BeiJing, China, {xuanzy,hguo,chen4chen,ame\_reiori,guanzhenyu}@buaa.edu.cn

BeiJing Institute of Satellite Information Engineering, BeiJing, China, xiyong.zhang@hotmail.com

Abstract. Montgomery modular multiplication is widely-used in public key cryptosystems (PKC) and affects the efficiency of upper systems directly. However, modulus is getting larger due to the increasing demand of computing and affects the efficiency of upper systems directly. computing cost. High-performance implementation of Montgomery modular multiplication is urgently required to ensure the highly-efficient operations in PKC. However, existing high-speed implementations still need a large amount redundant computing to simplify the intermediate result. Supports to the redundant representation is extremely limited on Montgomery modular multiplication. In this paper, we propose an efficient parallel variant of iterative Montgomery modular multiplication, called DRMMM, that allows the quotient can be computed in multiple iterations. In this variant, terms in intermediate result and the quotient in each iteration are computed in different radix such that computation of the quotient can be pipelined. Based on proposed variant, we also design high-performance hardware implementation architecture for faster operation. In the architecture, intermediate result in every iteration is denoted as three parts to free from redundant computations. Finally, to support FPGA-based systems, we design operators based on FPGA underlying architecture for better area-time performance. The result of implementation and experiment shows that our method reduces the output latency by 38.3% than the fastest design on FPGA.

**Keywords:** Montgomery modular multiplication, hardware implementation, parallel compression, pipeline, FPGA.

#### 1 Introduction

Modular multiplication computes  $AB \mod M$  for a multiplicand A, a multiplier B and a modulus M. As an essential primitive in PKC such as RSA[RSA78], elliptic curve cryptography (ECC)[Kob87], lattice-based cryptography (LBC)[MR09] and homomorphic encryption (HE)[Pai99], modular multiplication can well conceal information of the multiplicand and the multiplier. Due to a large number of modular multiplication operations in public key cryptosystems, the performance of modular multiplication significantly affects the performance of the upper cryptosystems. However, the bit width of the modulus is normally hundreds to thousands of bits to meet increasing security requirements, which makes modular multiplication costly. Therefore, high-performance implementation of modular multiplication is crucial to improve the performance of PKC.

In recent years, theoretical and implementation works have been proposed to improve the performance of modular multiplication. Modular multiplication includes two stages: multiplication and modular reduction. To speed up modular reduction, Barrett[Bar86] and Montgomery[Mon85] proposed division-free reduction algorithms applicable to any modulus, respectively. The algorithms replace division with cheaper operations such as shift, addition and multiplication. For some special moduli, their special mathematical properties are utilized to further simplify the process of modular reduction in [SWA12, Ber06, LN16]. These modular multiplication algorithms are applied according to application requirements in specific public key cryptosystems.

Works that optimize certain modular multiplication can be divided into two types: computation-prior works and speed-prior works. Among computation-prior works, multidigit multiplication [KO62, Too63] has been highly favored due to its reuse of intermediate calculation results. Works like [DLG18, DL19, APWK22, ASRS23] used original or modified multidigit multiplication algorithm to reduce computing cost of multiplication. However, reusing intermediate results would introduce more data dependencies into modular multiplication, which leads to high serialization. High-degree multidigit multiplication [DLG18] would introduce complex modular inverse and may dilute improvement on computation. These works can hardly take advantage of high parallelism and are more suitable for systems with limited parallelism.

Different from computation-prior works, speed-prior works take full advantage of parallelism and achieve extremely low output latency. Encode-compress structure is a common structure in parallel multiplier. Partial products (PPs) are generated by encoding and are accumulated by parallel compressor[Wal64, Dad90] in logarithmic time. Zhang et al.[ZCP22, ZCP24] constructed efficient encode-compress structure for generic modular multiplication algorithms. In their design, quotient and intermediate result of each iteration are computed by two encode-compress structures with same logic depth. Both two values are represented as a tuple to avoid costly long carry chain. Except encode-compress structure, other works focusing on parallelism improve time performance by carry save adders[EYÇ17] and pipeline[LRW<sup>+</sup>23]. Compared with computation-prior designs, speed-prior designs operate faster and take more resources.

Modular multiplication based on encode-compress structure can be considered as an iterative task. Each iteration includes PP generation and PP compression with certain compression ratio. In this case, the incomplete representation of compression result can save redundant intermediate computation as the degree of incompleteness increases. However, higher incompleteness complicates computation of the quotient. Previous designs only support representation with lower incompleteness. For tuple with three or more terms, complicated quotient computation breaks multi-path balance of existing structure and invalidates optimization of incomplete representation. Computation of the quotient becomes a bottleneck of the operation speed.

In addition, most of state-of-the-art hardware designs of modular multiplication only consider the application on application specific integrated circuits (ASICs) and only implement and simulate on field programmable gate arrays (FPGAs). As a flexible hardware platform with low development cost, FPGA has been one of mainstream platforms in parallel computing field. These designs can hardly achieve their best performance without considering the underlying properties of FPGA in FPGA-based systems.

To speed up computation of quotient in Montgomery modular multiplication (MMM), [ZCP22] proposed MMM algorithm that computes the quotient and intermediate result in each iteration in parallel. Based on the algorithm, an efficient encode-compress structure with two-tuple and an auxiliary bit was constructed. However, as the incomplete degree of the representation of intermediate increases, the balance of parallel computing paths between quotient and intermediate result is broken. For the representation as tuple with three or more terms, quotient is still the critical path of the whole algorithm. To fully

eliminate the adverse impact from the quotient, we hope that pipelined computing is allowed during computation of quotient and the data dependencies need to be further analyzed and broken.

In order to address above challenges, we analyze the algorithm structure of modular multiplication and the underlying architecture of FPGA. Based on the analysis, we propose a MMM variant that enables the quotient to be pipelined computed by DRMMM. Therefore, a faster encode-compress structure that supports larger tuple can be constructed. The main contributions of this paper are detailed as follows.

- 1. Different-radix MMM with high parallelism is proposed. In our proposed variant, computation of the quotient can be split into arbitrary iterations by a cross-iteration pipeline. By choosing proper stage number, computation of the quotient would no longer be the critical path in a iteration, which breaks the theoretical bottleneck of logic level.

- 2. Efficient encode-compress structure based on DRMMM is constructed. We represent the intermediate results as a tuple with three full-length terms for further improvement on time. In addition, we design efficient carry processing logic for our structure. With the help of proposed variant, at least two logic levels are saved in each iteration.

- 3. With all proposed methods mentioned above, we implement the multiplier and estimate its performance on FPGA platform. To better support FPGA-based system, we design high-performance LUT-based precomputed encode layer and 6-to-3 compressor. Compared with the state-of-the-art MMM design, our multiplier reduces output latency by 38.3% and reduces ATP by 34.04%.

The overview of this paper is presented as follows. Section 2 introduces preliminary about MMM and parallel compressor which is a part of parallel multiplier. In section 3 we propose our different-radix MMM variant and prove the correctness of the variant. The implementation structure for parallel system and two efficient operators based on LUT are proposed in section 4. Section 5 presents the result of implementation and experiment and section 6 concludes the paper.

# 2 Preliminary

#### 2.1 Montgomery Modular Multiplication

Let A, B be elements in residue system of modulus M. Modular multiplication computes the remainder r which satisfies  $r = A \times B - q \times M, 0 < r < M$ . To compute the quotient q, costly division is needed as equation described below.

$$q = \lfloor \frac{A \times B}{M} \rfloor \tag{1}$$

Montgomery modular multiplication (MMM) transforms the division into shifts and multiplications. The original version of MMM includes three  $n \times n$  multiplications and a n-bit shift, where n denotes the bit width of the modulus M. However, to avoid utilization of area-costly large-scale multipliers, most designs of MMM choose iterative version for better resource performance. Classical iterative MMM is described as Algorithm 1.

Notice that the output of MMM is "incorrect" since the output has a deviation  $r^{-d}$ . Let R be  $r^d$  and  $\mathrm{MMM}(A,B,M)$  denote the process of an MMM with inputs A,B,M. An extra modular multiplication is required to compute the correct result  $AB \mod M$ , which makes MMM less efficient than BMM when computing a single independent modular

```

Algorithm 1: Classical radix-2^k MMM

```

multiplication. The process of correcting is described below:

$$Z = \text{MMM}(A, B, M) = ABR^{-1} \mod M$$

$$\text{MMM}(Z, R^2, M) = AB \mod M$$

(2)

However, for continuous modular multiplication, instead of computing then correcting, we can transform elements in the ordinary domain (A) into elements in the Montgomery domain  $(\hat{A} = AR \mod M)$  such that the output  $\hat{Z}$  holds the Montgomery form as shown below:

$$\hat{Z} = \text{MMM}(AR, BR, M) = ABR \mod M \tag{3}$$

if all numbers in calculation is in Montgomery form, continuous modular multiplication can be computed without correction.

#### 2.2 Parallel Compression

Compression, actually accumulating multiple numbers is a frequently-used operation in data processing. Parallel compression is a kind of incomplete summation to avoid computing costly carry operations. For example, carry save adder (CSA) is a widely-used 3-to-2 compressor. Let X,Y,Z be input bits of a CSA, then output bits S,C are computed as described by (4) and (5):

$$S = X \oplus Y \oplus Z \tag{4}$$

$$C = XY \vee YZ \vee XZ \tag{5}$$

X, Y, Z, S, C satisfies equation S + 2C = X + Y + Z. For three *n*-bit numbers, *n* CSAs can compress them into two (n + 1)-bit numbers without dealing with carries of per bit by separating S, C calculated from each bit.

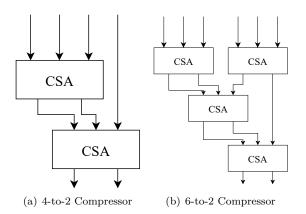

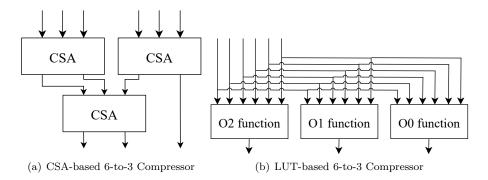

Cascaded CSAs can complete compression tasks with higher compression ratio. Figure 1 shows compressors based on CSA which can compress  $k \geq 3$  numbers into 2 numbers. For any compressors based on CSA, compressing k numbers needs k-2 groups of CSAs. The number of CSA in each group is related to the bit width of the numbers to be compressed in each layer. Therefore, implementing compressors with same compression ratio consumes almost identical resources. On the other hand, the arrangement structure of cascaded CSAs determines the compression performance. A linear arrangement can compress k numbers with O(k) CSA cell delays, while a balance ternary tree arrangement can compress

Figure 1: Compressors based on CSA.

k numbers with  $O(\log k)$  CSA cell delays. This ternary tree arrangement is Wallace tree which is commonly used in parallel multipliers.

Higher order counters were used to construct parallel multiplier by Dadda[Dad90]. A k-order counters can compress  $2^k - 1$  bits into k bits and thereby achieve compression with higher ratio. However, as order k increases, the complexity and depth of logic function that computes each output bit expand much more rapidly. A (7,3) counter, for instance, generates a 3-bit output with following equations for  $A_0, A_1, A_2, A_3, A_4, A_5, A_6$  as input bits:

$$\begin{cases}

O_0 = \bigoplus_{i=0}^{6} A_i \\

O_1 = \bigoplus_{i=0, j=1, j>i}^{i, j \le 6} A_i A_j \\

O_2 = \bigwedge_{i=0, j=1, k=2, j>i, k>j}^{i, j, k \le 6} \frac{A_0 A_1 A_2 A_3 A_4 A_5 A_6}{A_i A_j A_k}

\end{cases}$$

(6)

As described in equation (6), computation of each output bit is further complex compared with CSA. To achieve the best computation performance, balance between order and logical complexity is essential.

#### 3 Different-Radix MMM variant

In this section, we propose different-radix MMM variant with low data dependency. We analyze the data dependencies among algorithms with different radix. By introducing higher radix and shifts, we further break the data dependencies and allow the quotient q to be computed with a pipeline. With the help of the variant, computation of q can be distributed to several iterations, which is conducive to construct a faster iteration with less logic level.

#### 3.1 Overview of Proposed Variant DRMMM

Algorithm 2 shows our proposed variant. Instead of keeping same radix when computing  $q_i$  and  $a_iB$ , we compute  $a_iB$  and  $q_i$  with different radix such that  $q_i$  is independent from q in previous t iterations. Therefore, we can complete the computation of  $q_i$  in t iterations rather than one iteration.

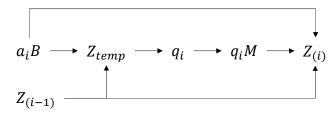

Firstly, a simple adjustment to the iteration structure is proposed based on in-iteration data dependencies. The in-iteration data dependencies of iterative MMM are shown in Figure 2. Notice that  $a_iB \to Z_{temp} \to q_i \to q_iM \to Z_{(i)}$  is the critical path in a iteration. The dependency between  $q_i$  and  $a_iB$  results in serial computations of  $a_iB$ ,  $q_i$  and  $q_iM$ .

### **Algorithm 2:** Proposed t-stage radix- $2^k$ MMM variant

```

Input: M is odd, 0 \le A, B < M, r = 2^k, A = (a_{d-1}, ..., a_1, a_0)_r,

M' = -M^{-1} \mod r^t, d = \lceil |M|/k \rceil, t \in \mathbb{N}

Output: Z_{out} = ABr^{-d} \mod M

1 \hat{Z}_{(-1)} = 0, \hat{q}_{(-1)} = 0, \hat{q}_{(-2)} = 0, ..., \hat{q}_{(-t)} = 0;

2 a_d = 0, a_{d+1} = 0, ..., a_{d+t} = 0;

3 for i = 0 to d + t do

4 \hat{q}_i = \text{MsPipeline}(\hat{Z}_{(i-1)} \mod r^t, M');

// \hat{q}_i = ((\hat{Z}_{(i-1)} \mod r^t)M' \mod r^t) >> k(t-1)

5 \hat{Z}_{(i)} = (\hat{Z}_{(i-1)} + a_iBr^t + \hat{q}_{(i-t)}M) >> k

6 end

7 Z_{out} = \hat{Z}_{(d+t)};

8 if Z_{out} \ge M then

9 \hat{Z}_{out} = Z_{out} - M;

10 end

11 return Z_{out} = ABr^{-d} \mod M

```

Figure 2: In-iteration data dependencies in iterative MMM.

To avoid serial computing, we break the data dependency between  $q_i$  and  $a_iB$  by a simple shift:

$$\begin{cases} \tilde{q}_i = (Z_{(i-1)} \mod r) \times M' \mod r \\ Z_{(i)} = (Z_{(i-1)} + a_i Br + \tilde{q}_i M)/r \end{cases}$$

$$(7)$$

where  $\tilde{q}_i$  is equivalent to  $q_{i-1}$  in line 4 of Algorithm 1. Computation of  $q_i$  and  $a_iB$  on which  $q_i$  depends are completed in neighbouring two iterations. With the adjustment, we can compute  $q_{(i-1)}M$  and  $a_iB$  in parallel with only one additional iteration.

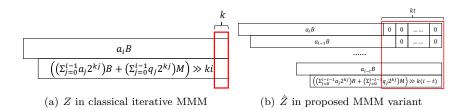

To further improve parallelism, we adjust the method to compute q. In each iteration, we simulate radix- $2^{tk}$  iterative MMM and compute MSBs of q in radix- $2^{tk}$  algorithm directly since cross-iteration dependency is weak in high-radix MMM. Concretely, in line 3 of Algorithm 2, we divide computation of  $\hat{q}_i$  and  $\hat{q}_iM$  into t iterations by a t-stage pipeline which spans t iterations, since  $q_i$  participates in calculation after t iterations. And when computing  $a_iB$ , a kt-bit shift is applied such that  $\hat{q}_i$  can be computed correctly. To show the difference of the computation of q, Figure 3 shows comparison of Z required when computing q. Compared with Algorithm 1,  $\hat{Z}$  in Algorithm 2 involves more  $a_iB$  terms and less  $q_iM$ .

#### 3.2 Cross-iteration Pipeline to Compute $\hat{q}$

The core of Algorithm 2 is computing  $\hat{q}$  by a cross-iteration pipeline. Since the computation of q is far more complex than updating Z, the pipeline needs to span multiple iterations. To ensure the computing correctness, for any  $i, j \in \mathbb{Z}$  satisfying |i-j| < t,  $q_i$  and  $q_j$  should be mutually independent.

**Figure 3:** Comparison of Z in each iteration.

The cross-iteration data dependencies of iterative MMM is analyzed as follows. In Algorithm 1, we have:

$$Z_{(i)}r = Z_{(i-1)} + a_i B + q_i M (8)$$

Let  $Z_{(-1)}$  equals to 0 and unfold equation (8) until only  $Z_{(-1)}$  remains. Then we have:

$$Z_{(i)}r^{i+1} = Z_{(-1)} + (\sum_{j=0}^{i} a_j r^j)B + (\sum_{j=0}^{i} q_j r^j)M$$

$$= (\sum_{j=0}^{i} a_j r^j)B + (\sum_{j=0}^{i} q_j r^j)M$$

(9)

Since  $a_i$ , B, M and r are known before first iteration, the cross-iteration data dependencies are all related to q. In other words, computation of  $q_i$  depends on all q computed in previous iterations. However, the number of iterations decreases with the increase of radix, and this leads to a periodic reduction of dependence degree of q on itself. For better quantitative analysis, based on the bit width ratio between known terms and dependent terms, cross-iteration dependence degree of MMM is defined as follows:

**Definition 1** (Cross-iteration dependence degree). Let  $r = 2^k$  be the radix of MMM,  $q_i$  be the quotient in *i*-th iteration,  $q_{-1} = 0$ , the cross-iteration dependence degree in *i*-th iteration  $\eta^{(i)}$  equals to:

$$\eta^{(i)} = \frac{\left| \left( \sum_{j=0}^{i-1} q_j r^j \right) M \right|}{\left| \left( \sum_{j=0}^{i} a_j r^j \right) B \right|}, i \in \mathbb{N}$$

(10)

Let  $|A| = |B| = |M| = N_M$  and  $|a_i| = |b_i| = |q_i| = |r| - 1 = k$ , the cross-iteration dependence degree is a function of i:

$$\eta^{(i)} = f(i) = \frac{i}{i+1} \tag{11}$$

where  $i \in \mathbb{N}$ ,  $i \leq \lceil \frac{N_M}{k} \rceil - 1$ . According to relationship of k and the number of iterations, we can estimate the upper bound of  $\eta^{(i)}$  as follows:

$$\eta^{(i)} \le \frac{\left(\left\lceil \frac{N_M}{k} \right\rceil - 1\right)}{\left\lceil \frac{N_M}{k} \right\rceil} = 1 - \frac{1}{\left\lceil \frac{N_M}{k} \right\rceil} \tag{12}$$

As k increases, the upper bound of  $\eta^{(i)}$  decreases. Higher-radix iterative MMM has less iterations, so its cross-iteration dependency is relatively weak. At an extreme, for instance, computation of q only depends on computation of AB in non-iterative MMM. Therefore, higher-radix algorithm computes  $q_i$  with less  $q_j$  computed in previous iterations.

**Figure 4:** Pipelined computation of  $\hat{q}$ .

| iteration    | Reg 1                               | Reg 2                             | <br>Reg t-2                       | Reg t-1                           | output                            |

|--------------|-------------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|

|              |                                     |                                   | <br>                              |                                   |                                   |

| <i>i-</i> th | $\hat{q}_i(\text{Stage 1})$         | $\hat{q}_{i-1}(\text{Stage 2})$   | <br>$\hat{q}_{i-t+1}$ (Stage t-2) | $\hat{q}_{i-t}(\text{Stage t-1})$ | $\longrightarrow \hat{q}_{i-t}$   |

|              | $\hat{q}_{i+1}(\text{Stage 1})$     | $\hat{q}_i(\text{Stage 2})$       | <br>$\hat{q}_{i-t+2}$ (Stage t-2) | $\hat{q}_{i-t+1}$ (Stage t-1)     | $\longrightarrow \hat{q}_{i-t+1}$ |

|              |                                     |                                   | <br>                              |                                   |                                   |

|              | $\hat{q}_{i+t}(\text{Stage 1})$     | $\hat{q}_{i+t+1}(\text{Stage 2})$ | <br>$\hat{q}_i(\text{Stage t-2})$ | $\hat{q}_{i-1}(\text{Stage t-1})$ | $\rightarrow \hat{q}_{i-1}$       |

| (i+t)-th     | $\widehat{q}_{i+t}(\text{Stage 1})$ | $\hat{q}_{i+t+1}(\text{Stage 2})$ | <br>$\hat{q}_{i+1}$ (Stage t-2)   | $\hat{q}_i(\text{Stage t-1})$     | $\longrightarrow \hat{q}_i$       |

|              |                                     |                                   | <br>                              |                                   |                                   |

**Figure 5:** Registers in the pipeline.

According to above analysis, we compute  $a_iB$  and  $q_{i-t}M$  in original radix and compute  $\hat{q}$  in higher radix to to eliminate dependencies between  $\hat{q}$  and previous q. In this case, computation of q only rely on  $\hat{Z}$  and  $a_iB$  rather than any intermediate result in adjacent t iterations. So a pipeline spanning t iterations is allowed to be constructed as shown in Figure 4.

To ensure the correctness of pipelined computing, computation of q should start t iterations in advance. We realize this by deferring the computation of Z for multiple iterations, i.e., by left shifts. Computation of q lasts t-1 iterations and registers in pipeline is shown in Figure 5. In final stage of the pipeline we compute qM since computing qM consumes same time as computing  $a_iB$ . With the help of the pipeline, computation of q is not a part of the critical path of an iteration any more.

### 3.3 Correctness Proof and Latency Analysis

Then we prove the correctness of Algorithm 2 and analyze its theoretical delay as follows.

#### 3.3.1 Correctness Proof

The correctness of a MMM algorithm can be evaluated by judging whether validity of right shift is satisfied and whether output is correct. We prove the correctness of Algorithm 2 through two conditions. Firstly, we prove the consistency of q in different radix iterative

MMM shown as Theorem 1. The theorem will help us to prove the shifting validity and output correctness.

**Theorem 1** (Consistency of q). Let d be the number of iterations and  $2^k$  be radix of MMM. Given the input A, B, M,  $\sum_{j=0}^{d-1} q_j r^j \mod 2^{|M|}$  in iterative MMM is a constant independent of k. The constant equals to  $ABM' \mod 2^{|M|}$ , where  $M' = -M^{-1} \mod 2^{|M|}$ .

*Proof.* As described in equation (9), in iterative MMM, we have :

$$Z_{(i)}r^{i+1} = (\sum_{j=0}^{i} a_j r^j)B + (\sum_{j=0}^{i} q_j r^j)M$$

(13)

After d iterations,  $Z_{(d-1)}$  satisfies:

$$Z_{(d-1)}r^{d} = AB + (\sum_{j=0}^{d-1} q_{j}r^{j})M$$

$$\Rightarrow Z_{(d-1)} = ABr^{-d} \mod M$$

(14)

Notice that  $|\sum_{j=0}^{d-1} q_j r^j| = kd$  since  $q_i$  is an element in residue system of modulus r. Now consider two outputs of different radix iterative MMM  $Z_{(d-1)}$  and  $\hat{Z}_{(\hat{d}-1)}$ . Then we have:

$$Z_{(d-1)}2^{kd} = AB + Q_1M (15)$$

$$\hat{Z}_{(\hat{d}-1)}2^{\hat{k}\hat{d}} = AB + Q_2M \tag{16}$$

Since  $d = \lceil \frac{|M|}{k} \rceil$ , |kd| ranges from |M| to |M| + k. In other words,  $|kd| \ge |M|$ ,  $|\hat{k}\hat{d}| \ge |M|$ . Hence  $Q_1$  and  $Q_2$  satisfy:

$$AB + Q_1 M \equiv 0 \bmod 2^{|M|} \tag{17}$$

$$AB + Q_2 M \equiv 0 \bmod 2^{|M|} \tag{18}$$

(17) - (18), then we get:

$$(Q_1 - Q_2)M \equiv 0 \bmod 2^{|M|} \tag{19}$$

Since M is odd,  $gcd(M, 2^{|M|}) = 1$ . Multiply  $M^{-1}$  on both sides and we have:

$$Q_1 \equiv Q_2 \bmod 2^{|M|} \tag{20}$$

And we obtain that  $Q_1 \mod 2^{|M|} = Q_2 \mod 2^{|M|}$ .

According to Theorem 1, we prove shifting validity and output correctness as shown in Theorem 2 and 3, respectively.

**Theorem 2** (shifting validity). The right shifting operation in Algorithm 2 discards no valid bit.

*Proof.* The proof of Theorem 2 is equivalent to prove that  $\hat{Z}_{(i-1)} + a_i B r^t + \hat{q}_{(i-t)} M \equiv 0 \mod r$  is met in every iteration. In Algorithm 1,  $q_i$  is computed from the LSBs of  $Z_{temp}$  which is shown within the red box in Figure 3(a). In residue system of modulus r,  $q_i$  and  $Z_{temp}$  satisfy:

$$Z_{temp} + q_i M \equiv Z_{temp} + (Z_{temp} M' \mod r) M \mod r$$

$$\equiv Z_{temp} (1 + MM') \mod r$$

$$\equiv Z_{temp} r r^{-1} \mod r$$

$$\equiv 0 \mod r$$

(21)

Therefore, right shift in Algorithm 1 does not discard any valid number. Now consider the Algorithm 2. According to Figure 3(b), we have:

$$\hat{Z}_{(i-1)}r^{i-t} = \left(\sum_{j=0}^{i} a_j r^j\right) B + \left(\sum_{j=0}^{i-t-1} q_j r^j\right) M

= \left(\sum_{j=0}^{i-t-1} a_j r^j\right) B + \left(\sum_{j=0}^{i-t-1} q_j r^j\right) M + \left(\sum_{j=i-t}^{i} a_j r^j\right) B$$

(22)

Let Q be the output of line 3 in Algorithm 2 without shift. The red box in Figure 3(b) denotes the input when computing Q. With the help of Theorem 1, we obtain:

$$Q = q_{i-1}||q_{i-2}||...||q_{i-t}$$

(23)

Thus  $\hat{q}_i$  equals to  $q_{i-1}$  in Algorithm 1. Naturally, we have:

$$\hat{Z}_{(i-1)} + a_i B r^t + \hat{q}_{i-t} M \equiv \hat{Z}_{(i-1)} + \hat{q}_{i-t} M \mod r$$

$$\equiv Z_{(i-t)} + (\sum_{j=i-t+1}^{i} a_j r^{j-i+t}) B$$

$$+ \hat{q}_{i-t} M \mod r$$

$$\equiv Z_{(i-t)} (1 + M M') \mod r$$

$$\equiv Z_{(i-t)} r r^{-1} \mod r$$

$$\equiv 0 \mod r$$

(24)

Therefore,  $\hat{Z}_{(i-1)} + a_i B r^t + \hat{q}_{(i-t)} M \equiv 0 \mod r$  always holds.

**Theorem 3** (output correctness). The output of Algorithm 2 equals to the output of Algorithm 1.

*Proof.* Let  $Z_{origin}$  be the output of Algorithm 1 and  $Z_{out}$  be the output of Algorithm 2. In final iteration, we have:

$$Z_{origin}r^d = AB + Q_1M (25)$$

$$Z_{out}r^{d+t} = ABr^t + \hat{Q}_2M = ABr^t + Q_2Mr^t \tag{26}$$

As proved in Theorem 1,  $Q_1$  equals to  $Q_2$ . So evidently,  $Z_{out} = Z_{origin}$ .

#### 3.3.2 Latency Analysis

Now let us analyze the theoretical delay of the variant in detail. Let  $T_m$  be the delay of a multiplication,  $T_a$  be the delay of an addition. In Algorithm 1,  $Z_{(i)} = Z_{(i-1)} + a_i B$ ,  $q_i = (Z_{(i)} \mod r)M' \mod r$ ,  $Z_{(i)} = (Z_{(i)} + q_i M) >> k$  are computed in serial. Since right shift is free, theoretical single iteration delay of Algorithm 1 can be described as follows:

$$t_c = (T_m + T_a) + T_m + (T_m + T_a + 0) = 3T_m + 2T_a$$

(27)

There are d iterations in Algorithm 1. Let  $T_{red}$  be the delay of final reduction, the output delay of Algorithm 1 is shown as follows:

$$T_{serial} = dt_c + T_{red} = 3dT_m + 2dT_a + T_{red}$$

$$\tag{28}$$

While in our proposed DRMMM variant,  $a_i B$  and  $\hat{q}_{(i-t)} M$  are computed in parallel. In addition, by cross-iteration pipeline, the multiplication in line 4 of Algorithm 2 is divided

into several parts which are distributed to several continuous iterations. The impact of q on the critical path of the iteration can be completely eliminated by choosing proper t and the critical path become  $a_i B(\hat{q}_{(i-t)}M) \to \hat{Z}_{(i)}$ . Therefore theoretical single iteration delay of Algorithm 2 become:

$$t_i = T_m + 2T_a \tag{29}$$

the output delay of Algorithm 2 can be described as follows:

$$T_{proposed} = (d+t+1)t_i + T_{red} = (d+t+1)T_m + 2(d+t+1)T_a + T_{red}$$

(30)

The difference between two theoretical delay is  $2dT_m - (t+1)(T_m + 2T_a)$ . When d is large, proposed variant computes faster and has higher parallelism.

We can observe that Algorithm 2 shortens the length of the critical path of single iteration by introducing extra iterations. As a configurable parameter, parameter t can control the length of the critical path of single iteration flexibly. In addition, parameter t also has a upper bound  $t_{max}$  since the critical path of single iteration would never be shorter than  $a_i B(\hat{q}_{(i-t)}M) \to \hat{Z}_{(i)}$ . When  $t > t_{max}$ , the delay of an iteration would not decrease with t increasing.

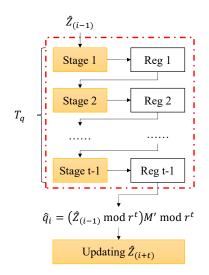

Let  $T_u$  be the output latency of updating  $\hat{Z}$  in line 4 of Algorithm 2 and  $T_q$  be the total delay to compute  $\hat{q}$  as described in line 3 of Algorithm 2.  $T_q$  is related to t. If there exists a pair of number  $k \in \mathbb{Z}^+$  and  $t \in \mathbb{Z}^+$  such that  $T_q \leq (t-1)T_u$ , computation of q can be completely removed from the critical path and parameter t achieve its upper bound  $t_{max}$ . The pair (k,t) always exists in proposed computing architecture as described in section 4.1. Our method provide a flexible parallelism for MMM algorithm by introducing parameter t. DRMMM allows designers to customize the length of the critical path of an iteration according to requirements of actual design.

### 4 Hardware Architecture for DRMMM

In this section, we propose a high-performance hardware implementation architecture for the new proposed DRMMM in section 4.1. To better support FPGA-based system, two LUT-based operators are proposed in section 4.2. Section 4.3 further explains key computation steps in proposed architecture. In addition, we also instantiate the architecture and construct a high-performance multiplier in section 4.3.

### 4.1 Overview of Proposed Hardware Architecture

In Algorithm 2, there are plenty of multiplications and additions with large bit width, where a large number of long carry chains are required to deal with in each iteration. These long carry chains would hinder the efficient computing. Therefore, we construct our high-performance Montgomery modular multiplier avoiding redundant intermediate computations. By replacing the addition and multiplication with proposed efficient operators, the implementation version of Algorithm 2 is presented in Algorithm 3.

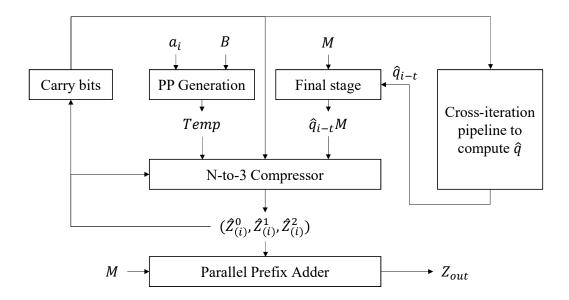

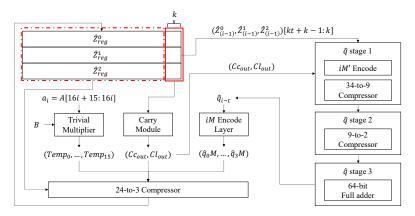

The hardware architecture based on Algorithm 3 is shown in Figure 6. Concretely, in each iteration, both  $a_iB$  and  $\hat{q}_{(i-t)}M$  are presented as a tuple with several terms. The number of terms depends on the encoding algorithm. When generating Temp, we choose trivial array multiplication and generate k partial products and use precomputing method when generating  $\hat{q}M$ . Booth multiplication and other methods are also adaptive to generate partial products. However, extra error analysis is required when using booth multiplication since booth method encodes unsigned integers to signed integers. Whatever the choice of encoding method, processes of "PP generation", "Final stage" and "Carry bit" should have equal logic levels.

Algorithm 3: Hardware implementation version of proposed MMM variant

```

Input: M is odd, 0 \le A, B < M, r = 2^k, A = (a_{d-1}, ..., a_1, a_0)_r,

M' = -M^{-1} \mod r^t, d = \lceil |M|/k \rceil, t \in \mathbb{N}

Output: Z_{out} = ABr^{-d} \mod M

1 \hat{Z}_{(-1)}^0 = \hat{Z}_{(-1)}^1 = \hat{Z}_{(-1)}^1 = 0;

2 \hat{q}_{-1}^1 = q_{-1}^2 = \dots = q_{-1}^t = 0;

/* initialization */

\mathbf{3} for i=0 to d+t do

Temp = Mult(a_i, B) << kt;

\hat{q}_i^1 = \text{PipelineStage}_1(\hat{Z}_{(i-1)}^0[kt-1:0], \hat{Z}_{(i-1)}^1[kt-1:0], \hat{Z}_{(i-1)}^2[kt-1:0]);

\hat{q}_i^2 = \text{PipelineStage}_2(\hat{q}_{i-1}^1);

\hat{q}_i^t = \text{PipelineStage}_t(\hat{q}_{i-1}^{t-1}) = \hat{q}_{(i-t)}M;

(\hat{Z}_{(i)}^{0}, \hat{Z}_{(i)}^{1}, \hat{Z}_{(i)}^{2}) = \text{Update}(Temp, \hat{q}_{i}^{t}, \hat{Z}_{(i-1)}^{0}, \hat{Z}_{(i-1)}^{1}, \hat{Z}_{(i-1)}^{2});

10 end

11 Z_{out} = \hat{Z}_{(d+t)};

12 if Z_{out} \ge M then

13 Z_{out} = Z_{out} - M

/* final reduction */

15 return Z_{out} = ABr^{-d} \mod M

```

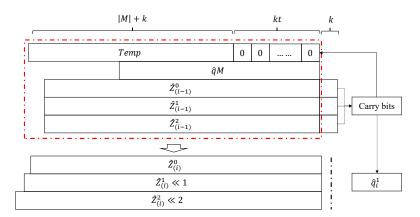

In the architecture, we optimize the representation of Z for lower iteration delay.  $\hat{Z}_{(i)}$  is divided into three parts  $\hat{Z}^0_{(i)}$ ,  $\hat{Z}^1_{(i)}$ ,  $\hat{Z}^2_{(i)}$  which satisfy  $\hat{Z}_{(i)} = \hat{Z}^0_{(i)} + \hat{Z}^1_{(i)} + \hat{Z}^2_{(i)}$ . In DRMMM, updating Z includes two stages: compression and shift. When compressing, we perform an incomplete compression and keep the tuple form such that no addition is required in each iteration. Shifts are performed in block "Carry bit". Instead of summation and shift, we compute the carry bits that are generated in summation directly by a logic module. Detailed description of the logic module is presented in section 4.3.

With the help of cross-iteration pipeline structure, Algorithm 3 can customize the computation of  $\hat{q}$ . Computation of each stage in the pipeline depends on computation cost of computing Temp and updating  $\hat{Z}$ . When computing  $\hat{q}$ , we utilize encode-compress structure which is split into t stages. In line 3 of Algorithm 2, as the stage number t increases, the number of PPs which compose  $\hat{q}$  appears linear growth. Meanwhile, parallel compressor can compress n PPs in  $O(\log n)$  levels. Therefore, there always exists a integer t such that the max delay of stages in the pipeline is less than delay of encoding and compressing related to  $\hat{Z}$ . In addition, the computation of q mainly includes operations pipelining friendly such as encoding, compressing and summation. A further explanation is presented in section 4.3.

In our design, both parallel prefix adder (PPA)[LD94] and ripple carry adder (RCA) are used. Due to the hardcore of lookahead carry logic set in slice, RCA is faster than PPA. However, RCA is unfriendly to pipeline since extra computation is introduced when pipelining. So we use RCA in non-pipelined scenario and multi-stage PPA is utilized when performing large scale summation such as final summation and final reduction. In general, our design has higher design flexibility and supports multiple design requirements.

#### 4.2 LUT-Based High-Performance Operators on FPGA

LUTs are basic logic units of FPGA. For a k-input one-output bool function, LUT implements the function by precomputing all outputs for any possible inputs and storing these outputs into a k-bit ROM. The value in ROM, denoted INIT, is the initial value of the

Figure 6: Proposed efficient hardware architecture.

LUT and input signals are used as an index to INIT. A LUT with k-bit ROM is a LUTk. According to the properties of LUTk, any k-input bool function can be implemented by a single LUTk. For common FPGA devices, the size of LUT ranges from 4 to 6.

Let us take LUT6 as an instance. As the basic logic unit of most of FPGA, LUT6 can be configured as a 6-input 1-output function or a 5-input 2-output function. Since a LUT6 only has two output pins, a LUT6 cannot output more than 2 values. The physical property determines that different implementation methods based on LUT have different performance. Based on properities of LUT, two efficient opertors on FPGA are proposed as follows.

#### 4.2.1 LUT-Based Precomputed Encoding Layer

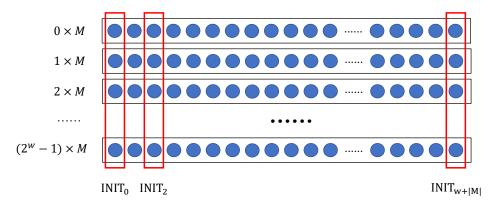

Inspired by modular multiplication for special modulus, we generalize the design idea of embeding modulus to DRMMM. By combining the fixed window slicing method with computation of q and qM, we precompute iM' mod  $2^w$  and iM where  $i \in [0, 2^w)$ . Considering the cost of storage and looking up from a table, we utilize LUTs to store precomputed values and construct the LUT-based precomputed encoding layer. With the help of encoding layer, we reduce the number of input signals significantly such that the speed of the multiplier increases.

Figure 7 shows how we construct the encoding layer. The values of  $iM(iM' \mod 2^w)$  are precomputed first and arranged from small to large as shown in Figure 7. Then we rotate this matrix 90 degrees clockwise and assign the value of each row in the new matrix to  $\text{INIT}_i$  as shown in red box. The size of window w should less than k since a LUTk cannot store more than  $2^k$  bits. Otherwise, cascaded LUTs are introduced to look up values from a larger table. Not only that, as w increases, the number of required large-scale multiplexers increase rapidly, which results in an exponential growth of lookup cost. Thus we also limit the size of window w within [4,6] in our design.

Now let us discuss the merge of tables. In radix- $2^k$  MMM, computation of q and qM can be viewed as a k-to-k mapping and a k-to-k|M| mapping for certain modulus, respectively. Naturally, the two serial mappings can be combined into a new k-to-k|M| mapping without any extra process. If the merge is applied, the new mapping would

Figure 7: LUT-based iM encoding layer.

complete the computation of qM with the latency of one mapping. However, the merge of mappings is not efficient for all k. In Algorithm 3, the q mapping and M mapping are divided into several parts in order to avoid the use of large-scale multiplexers. Since each output bit is related to all input bits, combined mapping can only be regarded as a whole to ensure the correctness of computing. Once the q mapping and M mapping are combined, the new mapping can not be divided any more. This limitation reduces the flexibility of the design and makes it harder to balance the latency of every parallel path. Therefore, we apply the merge only in the design of radix-4 multiplier.

#### 4.2.2 Advanced LUT-Based 6-to-3 Compressor

As shown in section 2.2, the cell of parallel compressors is actually a counter. For any  $n \in \mathbb{N}^+$ , we can construct a  $(2^n - 1, n)$  counter as a cell of a parallel compressor. This motivates us to design a cell with higher compression ratio based on LUT.

The logic of our compressor cell is presented as follows:

$$\begin{cases}

O_0 = \bigoplus_{i=0}^{5} A_i \\

O_1 = \bigoplus_{i=0,j=1,j>i}^{i,j \le 5} A_i A_j \\

O_2 = \bigwedge_{i=0,j=1,j>i}^{i,j \le 5} \frac{A_0 A_1 A_2 A_3 A_4 A_5}{A_i A_j}

\end{cases}$$

(31)

In equation (29),  $O_1$  and  $O_2$  have  $C_6^2$  terms, which seems to result in a huge logic level. Indeed, these logic functions are far more complex than two cascaded CSAs. Similar design should be avoided in an ASIC-based system. However, in FPGA-based system, our design is more efficient in terms of speed due to physical properties of LUTs.

Common parallel compressor tends to use CSA as a cell. However, limited by output pins, a LUT6 can only implement a CSA, although the implementation of CSA only needs 8 bits ROM. The hierarchy of CSA-based 6-to-3 compressor is shown in Figure 8(a). Three LUTs are required to build a 1-bit CSA-based 6-to-3 compressor.

Figure 8(b) shows the hierarchy of proposed LUT-based 6-to-3 compressor. As introduced at the beginning of section 4.2, a LUTk can implement any k-input bool function. Thus, each output signal in equation (29) can be computed by a single LUT6. Our compressor also requires 3 LUTs. Let  $T_l$  be the logic delay of a LUT,  $T_n$  be the net delay between LUTs. Output latency of design (a) is  $2T_l + T_n$ , while design (b) only needs  $T_l$  to output. In FPGA-based systems, proposed 6-3 compressor is 20% faster than CSA-based compressor.

**Figure 8:** Comparison of two implementations.

## Computation of $\hat{Z}$ and $\hat{q}$

In this subsection, we explain the process of updating  $\hat{Z}$  and computing  $\hat{q}$  by a t-stage pipeline in detail. At the end of section, an instance of our architecture is presented to highlight the optimization effectiveness.

### 4.3.1 Process of Updating $\hat{Z}$

Notice line 9 of Algorithm 3. Computation of  $\hat{Z}$  consists of two parts: compression and shift. We analyze the compression first. According to the analysis of Algorithm 3 at the beginning of section 4, we know that |Temp| = kt + |M| + k. Values in Temp are longest among input signals of function Update(·). So we set the length of  $\hat{Z}_{(i)}^0$ ,  $\hat{Z}_{(i)}^1$  and  $\hat{Z}_{(i)}^2$  to kt + |M| + k + f(k, w) such that compression can be performed correctly, where f(k, w)denotes the compression level. Figure 9 shows the process of updating  $\hat{Z}$ . The red box denotes terms to be compressed.

When updating  $\hat{Z}$ , a k-bit right shift is performed since the least k significant bits are all 0. However, in the triplet  $(\hat{Z}^0, \hat{Z}^1, \hat{Z}^2)$ , shifting directly may cause the loss of carry bits. To address this issue, we design a logic module as shown on the right of Figure 9 to compute carry bits of the triplet. The triplet may produce two carry bits and the two to compute carry bits of the triplet. The triplet may produce two carry bits and the two carry bits are only related to  $\hat{Z}^0_{(i)}[k-1:k-2]$ ,  $\hat{Z}^1_{(i)}[k-1:k-2]$  and  $\hat{Z}^2_{(i)}[k-1:k-2]$ , since for a k-bit integer n, |3n|=k+2 when  $k\geq 2$ . Recall line 4 of Algorithm 2, that means,  $\hat{Z}^0_{(i)}[k-1:0]+\hat{Z}^1_{(i)}[k-1:0]+\hat{Z}^2_{(i)}[k-1:0]\equiv 0 \mod 2^k$  always holds in each iteration. Then we give a detailed discussion to show all possible values of carry bits. Let  $n_m$  be  $\hat{Z}^0_{(i)}[k-1]+\hat{Z}^1_{(i)}[k-1]+\hat{Z}^1_{(i)}[k-1]$  and  $n_l$  be  $\hat{Z}^0_{(i)}[k-2]+\hat{Z}^1_{(i)}[k-2]+\hat{Z}^1_{(i)}[k-2]$ . In order to facilitate, let  $\hat{Z}_l$  be  $\hat{Z}^0_{(i)}[k-1:0]+\hat{Z}^1_{(i)}[k-1:0]+\hat{Z}^1_{(i)}[k-1:0]$ . We first

consider the LSB of carry  $C_l$ . This bit is easy to compute since if  $n_m + n_l = 0$ ,  $|\hat{Z}_l| \leq k$ always holds and we have  $\hat{Z}_l < 2^k$ . Thus  $\hat{Z}_l$  equals to 0 since  $\hat{Z}_l \equiv 0 \mod 2^k$ . In a word, the carry bit with lower weight is computed as follows:

$$C_{l} = \hat{Z}_{(i)}^{0}[k-1]|\hat{Z}_{(i)}^{1}[k-1]|\hat{Z}_{(i)}^{2}[k-1]|\hat{Z}_{(i)}^{0}[k-2]$$

$$|\hat{Z}_{(i)}^{1}[k-2]|\hat{Z}_{(i)}^{2}[k-2]$$

(32)

The MSB of carry  $C_m$  is much more complex to compute.  $C_m = 1$  holds on the condition that a carry bit with weight of k+1 must be generated from  $\hat{Z}_{(i)}^0[k-1:k-2], \hat{Z}_{(i)}^1[k-1:k-2]$ (k-2),  $\hat{Z}_{(i)}^2[k-1:k-2]$  and at the same time, there must be a bit remaining among the six bits after generating the carry bit. With the help of  $n_m$  and  $n_l$ , all the case of  $C_m$  are shown as follows:

**Figure 9:** Process of Updating  $\hat{Z}$ .

- 1.  $n_m = 3, n_l = 0/1/2/3$ . When  $n_m = 3$ , the condition is always satisfied no matter what  $n_l$  is. After generating required carry bit,  $n_m = 1$  and there must be another carry bit, namely  $C_m$  generated.

- 2.  $n_m = 2, n_l = 3/2/1$ . Although  $n_m = 0$  after generating required carry bit,  $n_l$  remains.  $C_m = 1$  in this case.

- 3.  $n_m = 2, n_l = 0$ . After generating required carry bit,  $n_m + n_l = 0$ . There is no bit remaining so  $C_m = 0$ .

- 4.  $n_m = 1, n_l = 3$ . Same as the condition that  $n_m = 2, n_l = 1, C_m = 1$ .

- 5.  $n_m = 1, n_l = 2$ . Same as the condition that  $n_m = 2, n_l = 0, C_m = 0$ .

- 6. Others. These cases cannot generate required carry bit and  $C_m = 0$  in these cases.

We use two parallel LUTs to compute  $C_l$  and  $C_m$ . The INIT of two LUTs are "0xffffffffffff" and "0xfffefe80fe808000", respectively.

#### 4.3.2 Process of Computing $\hat{q}$

The computation of  $\hat{q}$  is actually pipelined implementation of  $(\hat{Z}_{(i-1)} \bmod r^t)M' \bmod r^t) >> k(t-1)$ . As algorithm parameters changes, the structure of pipeline also changes. Here we present the computing task of our pipeline. The  $\hat{q}$  computing process consists of following steps: a) compute  $\hat{Z}_{(i-1)}M'$  with the help of iM' encoding layer. Let w' be the window size of iM' encoding layer.  $3 \times \lceil kt/w' \rceil$  terms are generated after encoding. b) sum all  $3 \times \lceil kt/w' \rceil$  terms by parallel compressor. Then perform the final summation by cascade ternary adder or trivial adder. This process may span several iterations since accumulation is costly. c) compute  $\hat{q}M$  with the help of iM encoding layer. Let w be the window size of iM encoding layer.  $\lceil k/w \rceil$  terms are generated after encoding.

#### 4.3.3 An Instance of DRMMM

Here we give the hardware structure of proposed multiplier in Figure 10 to show our optimization on parallelism. In this multiplier, k = 16, t = 4 and all parts including  $a_i B$ , updating  $\hat{Z}$ , qM and all stages of  $\hat{q}$  pipeline are operated in parallel.

Let  $T_l$  be delay of one LUT (including both logic and net). In Figure 10, the delay of trivial multiplier, carry module and iM encode layer are  $T_l$ . A 24-to-3 compressor, based

**Figure 10:** Proposed radix-16 4-stage multiplier.

on our advance 6-to-3 compressor, has a delay of  $3T_l$  since we can construct a complete binary tree using 6-to-3 compressor as a node. Therefore, the total delay of a iteration is  $4T_l$ . Since there is no data dependencies among stages of pipeline in a single iteration, we only need to control the delay of each stage under  $4T_l$ . Stage 1 precedes carry module so we have only  $3T_l$  left. We perform iM' encode layer which costs  $T_l$  and a 2-level 34-to-9 compressor which costs  $T_l$ . In stage 2 we perform a 9-to-2 compressor whose delay is  $3T_l$ . In stage 3, we need to sum the two partial product and transfer MSBs of  $\hat{q}$  to stage 4, so a full adder is set here. The delay of full adder equals to  $T_l + 16T_{carry}$ , where  $T_{carry}$  is the delay of 4-bit carry chain. Due to the hardcore of lookahead carry chain embedded in slice of FPGA, carries are computed so fast that the delay of 64-bit full adder is still less than  $4T_l$ . Therefore in our radix-16 design, the critical path is always the computation of  $\hat{Z}$  in Figure 10 and the theoretical delay is only  $4T_l$ . Parallel prefix adder can be used in final reduction to keep system frequency at a high level.

#### 5 Performance of DRMMM

Proposed high-performance Montgomery modular multiplier was implemented with Verilog HDL. We perform the systhesis and implementation of the project with Xilinx Vivado default strategy on xc7v585tffg1157-3 device. Table 1 shows comparison between our multiplier and other designs on Virtex-7 FPGA.

Due to extensive use of parallel compressor, designs based on DRMMM is speed-prior and has relatively high area requirement. Meanwhile, our precomputed encoding layer reduces area to compute  $\hat{q}$  and  $\hat{q}M$ . To evaluate different parts in our methodology, we attempt different strategies to compute  $a_iB$  in our design and implement two multipliers with different structure.

Optimization of area is completely from the precomputation. In the radix-4 multiplier, a series of  $4 \times 4$  area-efficient sub-multipliers constructed in [URSK21] are used to compute  $a_i B$ , and  $\hat{q}, \hat{q} M$  are computed entirely by the precomputed encoding layer. The reduction of computing cost results in an obvious improvement on area. Compared with designs[ZCP22, PSY18, KDS21] with same radix, the radix-4 multiplier reduces the area by 33.4%, 37.2% and 29.4%, respectively.

On the other hand, to speed up MMM, we propose DRMMM and efficient hardware architecture based on it. In addition, LUT-based 6-to-3 parallel compressor is proposed to improve the time performance. Both algorithm structure and advanced compressor result in the improvement of speed, where our advanced compressor reduces compression level significantly and the structure enhances the incompleteness degree of compression and further frees computing resources from unnecessary calculation. Different from radix-4

| Design        | $N_M$ | k  | Time  |        | Area      |       |      |     | ATP   |         |

|---------------|-------|----|-------|--------|-----------|-------|------|-----|-------|---------|

|               |       |    | Cycle | Period | Total     | LUT   | FF   | DSP | Total | (in mg) |

|               |       |    | (cnt) | (ns)   | $(\mu s)$ | LUI   | rr   | DSF | Total | (in ms) |

| Ours          | 1024  | 4  | 268   | 2.70   | 0.72      | 10588 | 3261 | 0   | 13849 | 9.97    |

|               |       | 16 | 74    | 2.86   | 0.21      | 42179 | 4995 | 0   | 47174 | 9.91    |

| [ZCP22]       | 1024  | 4  | 264   | 3.00   | 0.79      | 17661 | 3120 | 0   | 20781 | 16.42   |

|               |       | 16 | 70    | 4.90   | 0.34      | 45087 | 3187 | 0   | 48274 | 16.41   |

| [PSY18]       | 1024  | 2  | 516   | 2.40   | 1.24      | 9015  | 3088 | 0   | 12103 | 15.01   |

|               |       | 4  | 262   | 3.96   | 1.04      | 16883 | 5165 | 0   | 22048 | 22.93   |

| [EYÇ17]       | 1024  | 2  | 530   | 2.23   | 1.18      | 9304  | 7492 | 0   | 16796 | 19.82   |

|               |       | 8  | 132   | 6.88   | 0.91      | 34904 | 7427 | 0   | 42331 | 38.52   |

| $[TLZ^+]$     | 1024  | -  | 535   | 3.93   | 2.10      | 4279  | -    | 15  | 10279 | 21.58   |

| $[LRW^{+}23]$ | 1024  | 4  | 261   | 3.95   | 1.03      | 2845  | 3165 | 24  | 15610 | 16.08   |

| [KDS21]       | 1024  | 4  | 257   | 17.54  | 4.50      | 16531 | 3098 | 0   | 19629 | 88.33   |

| [ZCP21]       | 1024  | 4  | 290   | 3 90   | 1 13      | 19124 | 4638 | 0   | 23762 | 26.85   |

Table 1: Comparison of different Montgomery Modular Multiplier on Virtex-7 FPGA

version, we replace sub-multipliers with a trivial array mapping to give full play to parallel design. Therefore, as analyzed in section 4.3, the radix-16 4-stage multiplier maxmizes the advantage of parallel design, which results in a minimal period with only 4 LUTs delay. Compared with the state-of-the-art multiplier[ZCP22, EYÇ17, LRW+23] in terms of speed, the radix-16 multiplier reduces output delay by 38.3%, 76.9% and 79.6%.

Our methodology provides flexible hardware implementation architecture suitable for multiple scenarios. Radix-4 multiplier shows great advantage on area performance. However, compared with parallel compressor, sub-multiplier has an unacceptable delay and can hardly give full play to parallel design. Although the balance between two parallel path is constructed, the speed of radix-4 version has only a weak improvement.

Similarly, in the radix-16 version, the output delay is reduced significantly, while the area is almost as same as the area of design with same radix[ZCP22]. Nonetheless, with all these optimization methods, our multiplier improves both area and time performance. Our design reduces ATP by 34.04%, 39.67% and 50.06% compared with least 3 ATP in Table 1, which shows the effectiveness of our method on FPGA platform.

### 6 Conclusion

In this paper, we analyzed the data dependencies of MMM and proposed an efficient parallel variant DRMMM. By computing  $a_iB$  and  $\hat{q}$  with different radix, the cross-iteration dependencies of  $\hat{q}$  is broken. The variant allows to compute  $a_iB$ ,  $\hat{q}$  and  $\hat{q}M$  in parallel and supports pipelined computation of  $\hat{q}$ . In addition, we proposed an efficient implementation architecture of the variant and implemented high-perfomance MM multiplier on FPGA platform. To further speed up the computation, the precomputed encode layer and advanced 6-to-3 compressor based on properties of LUT were proposed, which improves area and time performance on FPGA. Our proposed multiplier has advantages on both resource and speed. Compared with the state-of-the-art designs, our multiplier reduces output latency by 38.3% and ATP by 34.04% when implemented on FPGA.

# 7 Acknowledgement

This work was supported by the Beijing Natural Science Foundation (No.4242022), the CCF-NSFOCUS 'Kunpeng' Research Fund(No.CCF-NSFOCUS 2023006) and the National

Natural Science Foundation of China(No.62172025, No.U2241213).

### References

- [APWK22] Asep Muhamad Awaludin, Jonguk Park, Rini Wisnu Wardhani, and Howon Kim. A high-performance ecc processor over curve448 based on a novel variant of the karatsuba formula for asymmetric digit multiplier. *IEEE Access*, 10:67470–67481, 2022.

- [ASRS23] T Abirami, S Saravanan, A Rajeshkumar, and KM Santhosh. Fpga-based optimized design of montgomery modular multiplier using karatsuba algorithm. In 2023 Second International Conference on Electronics and Renewable Systems (ICEARS), pages 131–135. IEEE, 2023.

- [Bar86] Paul Barrett. Implementing the rivest shamir and adleman public key encryption algorithm on a standard digital signal processor. In *Conference on the Theory and Application of Cryptographic Techniques*, pages 311–323. Springer, 1986.

- [Ber06] Daniel J Bernstein. Curve25519: new diffie-hellman speed records. In Public Key Cryptography-PKC 2006: 9th International Conference on Theory and Practice in Public-Key Cryptography, New York, NY, USA, April 24-26, 2006. Proceedings 9, pages 207–228. Springer, 2006.

- [Dad90] L Dadda. Some schemes for parallel multipliers. IEEE Computer Society Press, 1990.

- [DL19] Jinnan Ding and Shuguo Li. A low-latency and low-cost montgomery modular multiplier based on nlp multiplication. *IEEE Transactions on Circuits and Systems II: Express Briefs*, 67(7):1319–1323, 2019.

- [DLG18] Jinnan Ding, Shuguo Li, and Zhen Gu. High-speed ecc processor over nist prime fields applied with toom–cook multiplication. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 66(3):1003–1016, 2018.

- [EYÇ17] Serdar Süer Erdem, Tuğrul Yanık, and Anıl Çelebi. A general digit-serial architecture for montgomery modular multiplication. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, 25(5):1658–1668, 2017.

- [KDS21] Venkata Reddy Kolagatla, Vivian Desalphine, and David Selvakumar. Areatime scalable high radix montgomery modular multiplier for large modulus. In 2021 25th International Symposium on VLSI Design and Test (VDAT), pages 1–4. IEEE, 2021.

- [KO62] Anatolii Alekseevich Karatsuba and Yu P Ofman. Multiplication of manydigital numbers by automatic computers. In *Doklady Akademii Nauk*, volume 145, pages 293–294. Russian Academy of Sciences, 1962.

- [Kob87] Neal Koblitz. Elliptic curve cryptosystems. Mathematics of computation, 48(177):203-209, 1987.

- [LD94] Sivaramakrishnan Lakshmivarahan and Sudarshan K Dhall. *Parallel computing using the prefix problem.* Oxford University Press, 1994.

- [LN16] Patrick Longa and Michael Naehrig. Speeding up the number theoretic transform for faster ideal lattice-based cryptography. In *Cryptology and Network Security: 15th International Conference, CANS 2016, Milan, Italy, November 14-16, 2016, Proceedings 15*, pages 124–139. Springer, 2016.

- [LRW<sup>+</sup>23] Hongshuo Li, Shiwei Ren, Weijiang Wang, Jingqi Zhang, and Xiaohua Wang. A low-cost high-performance montgomery modular multiplier based on pipeline interleaving for iot devices. *Electronics*, 12(15):3241, 2023.

- [Mon85] Peter L Montgomery. Modular multiplication without trial division. *Mathematics of computation*, 44(170):519–521, 1985.

- [MR09] Daniele Micciancio and Oded Regev. Lattice-based cryptography. In *Post-quantum cryptography*, pages 147–191. Springer, 2009.

- [Pai99] Pascal Paillier. Public-key cryptosystems based on composite degree residuosity classes. In *International conference on the theory and applications of cryptographic techniques*, pages 223–238. Springer, 1999.

- [PSY18] Jeng-Shyang Pan, Pengfei Song, and Chun-Sheng Yang. Efficient digit-serial modular multiplication algorithm on fpga. *IET Circuits, Devices & Systems*, 12(5):662–668, 2018.

- [RSA78] Ronald L Rivest, Adi Shamir, and Leonard Adleman. A method for obtaining digital signatures and public-key cryptosystems. *Communications of the ACM*, 21(2):120–126, 1978.

- [SWA12] Suhas Sreehari, Huapeng Wu, and Majid Ahmadi. Fast modular reduction for large-integer multiplication for cryptosystem application. In 2012 Second International Conference on Digital Information and Communication Technology and it's Applications (DICTAP), pages 226–229. IEEE, 2012.

- [TLZ<sup>+</sup>] Qiqi Tao, Liying Li, Junlong Zhou, Guitao Cao, and Dan Meng. Cognizant resource balancing in montgomery modular multiplication optimization for dsp. Available at SSRN 4689722.

- [Too63] Andrei L Toom. The complexity of a scheme of functional elements realizing the multiplication of integers, published in soviet math (translations of dokl. adad. nauk. sssr), 4, 1963.

- [URSK21] Salim Ullah, Semeen Rehman, Muhammad Shafique, and Akash Kumar. High-performance accurate and approximate multipliers for fpga-based hardware accelerators. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 41(2):211–224, 2021.

- [Wal64] Christopher S Wallace. A suggestion for a fast multiplier. *IEEE Transactions* on electronic Computers, (1):14–17, 1964.

- [ZCP21] Bo Zhang, Zeming Cheng, and Massoud Pedram. High-radix design of a scalable montgomery modular multiplier with low latency. *IEEE Transactions on Computers*, 71(2):436–449, 2021.

- [ZCP22] Bo Zhang, Zeming Cheng, and Massoud Pedram. An iterative montgomery modular multiplication algorithm with low area-time product. *IEEE Transactions on Computers*, 72(1):236–249, 2022.

- [ZCP24] Bo Zhang, Zeming Cheng, and Massoud Pedram. Design of a high-performance iterative barrett modular multiplier for crypto systems. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, 2024.